# SN54LVT8980, SN74LVT8980 EMBEDDED TEST-BUS CONTROLLERS

# IEEE STD 1149.1 (JTAG) TAP MASTERS WITH 8-BIT GENERIC HOST INTERFACES

SCBS676C - DECEMBER 1996 - REVISED AUGUST 1997

- Members of Texas Instruments (TI) Broad Family of Testability Products Supporting IEEE Std 1149.1-1990 (JTAG) Test Access Port (TAP) and Boundary-Scan Architecture

- Provide Built-In Access to IEEE Std 1149.1

Scan-Accessible Test/Maintenance

Facilities at Board and System Levels

- While Powered at 3.3 V, the TAP Interface is Fully 5-V Tolerant for Mastering Both 5-V and/or 3.3-V IEEE Std 1149.1 Targets

- Simple Interface to Low-Cost 3.3-V

Microprocessors/Microcontrollers Via 8-Bit

Asynchronous Read/Write Data Bus

- Easy Programming Via Scan-Level

Command Set and Smart TAP Control

- Transparently Generate Protocols to Support Multidrop TAP Configurations Using TI's Addressable Scan Port

- Flexible TCK Generator Provides Programmable Division, Gated-TCK, and Free-Running-TCK Modes

- Discrete TAP Control Mode Supports Arbitrary TMS/TDI Sequences for Non-Compliant Targets

- Programmable 32-Bit Test Cycle Counter Allows Virtually Unlimited Scan/Test Length

- Accommodate Target Retiming (Pipeline)

Delays of Up to 15 TCK Cycles

- Test Output Enable (TOE) Allows for External Control of TAP Signals

- High-Drive Outputs (-32-mA I<sub>OH</sub>, 64-mA I<sub>OL</sub>) at TAP Support Backplane Interface and/or High Fanout

- Package Options Include Plastic Small-Outline (DW) Package, Ceramic Chip Carriers (FK), and Ceramic 300-mil DIPs (JT)

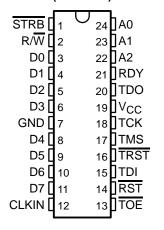

#### SN54LVT8980 ... JT PACKAGE SN74LVT8980 ... DW PACKAGE (TOP VIEW)

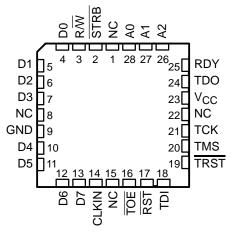

# SN54LVT8980 . . . FK PACKAGE (TOP VIEW)

NC - No internal connection

# description

The 'LVT8980 embedded test-bus controllers (eTBC) are members of the TI broad family of testability integrated circuits. This family of devices supports IEEE Std 1149.1-1990 boundary scan to facilitate testing of complex circuit assemblies. Unlike most other devices of this family, the eTBC is not a boundary-scannable device; rather, its function is to master an IEEE Std 1149.1 (JTAG) test access port (TAP) under the command of an embedded host microprocessor/microcontroller. Thus, the eTBC enables the practical and effective use of the IEEE Std 1149.1 test-access infrastructure to support embedded/built-in test, emulation, and configuration/maintenance facilities at board and system levels.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SCBS676C - DECEMBER 1996 - REVISED AUGUST 1997

## description (continued)

The eTBC masters all TAP signals required to support one 4- or 5-wire IEEE Std 1149.1 serial test bus – test clock (TCK), test mode select (TMS), test data input (TDI), test data output (TDO), and test reset (TRST). All such signals can be connected directly to the associated target IEEE Std 1149.1 devices without need for additional logic or buffering. However, as well as being directly connected, the TMS, TDI, and TDO signals can be connected to distant target IEEE Std 1149.1 devices via a pipeline, with a retiming delay of up to 15 TCK cycles; the eTBC automatically handles all associated serial-data justification.

Conceptually, the eTBC operates as a simple 8-bit memory- or I/O- mapped peripheral to a microprocessor/microcontroller (host). High-level commands and parallel data are passed to/from the eTBC via its generic host interface, which includes an 8-bit data bus (D7–D0) and a 3-bit address bus (A2–A0). Read/write select (R/W) and strobe (STRB) signals are implemented so that the critical host-interface timing is independent of the CLKIN period. An asynchronous ready (RDY) indicator is provided to hold off, or insert wait states into, a host read/write cycle when the eTBC cannot respond immediately to the requested read/write operation.

High-level commands are issued by the host to cause the eTBC to generate the TMS sequences necessary to move the test bus from any stable TAP-controller state to any other such stable state, to scan instruction or data through test registers in target devices, and/or to execute instructions in the Run-Test/Idle TAP state. A 32-bit counter can be programmed to allow a predetermined number of scan or execute cycles.

During scan operations, serial data that appears at the TDI input is transferred into a serial-to- $4 \times 8$ -bit-parallel first-in/first-out (FIFO) read buffer, which can then be read by the host to obtain the return serial-data stream up to eight bits at a time. Serial data that is to be transmitted from the TDO output is written by the host, up to eight bits at a time, to a  $4 \times 8$ -bit-parallel-to-serial FIFO write buffer.

In addition to such simple state-movement, scan, and run-test operations, the eTBC supports several additional commands that provide for input-only scans, output-only scans, recirculate scans (in which TDI is mirrored back to TDO), and a scan mode that generates the protocols used to support multidrop TAP configurations using TI's addressable scan port. Two loopback modes also are supported that allow the microprocessor/microcontroller host to monitor the TDO or TMS data streams output by the eTBC.

The eTBC's flexible clocking architecture allows the user to choose between free-running (in which the TCK always follows CLKIN) and gated modes (in which the TCK output is held static except during state-move, run-test, or scan cycles) as well as to divide down TCK from CLKIN. A discrete mode is also available in which the TAP is driven strictly by read/write cycles under full control of the microprocessor/microcontroller host. These features ensure that virtually any IEEE Std 1149.1 target device or device chain – even where such may not fully comply to IEEE Std 1149.1 – can be serviced by the eTBC.

While most operations of the eTBC are synchronous to CLKIN, a test-output enable ( $\overline{\text{TOE}}$ ) is provided for output control of the TAP outputs, and a reset ( $\overline{\text{RST}}$ ) input is provided for hardware reset of the eTBC. The former can be used to disable the eTBC so that an external controller can master the associated IEEE Std 1149.1 test bus.

The SN54LVT8980 is characterized for operation over the full military temperature range of –55°C to 125°C. The SN74LVT8980 is characterized for operation from –40°C to 85°C.

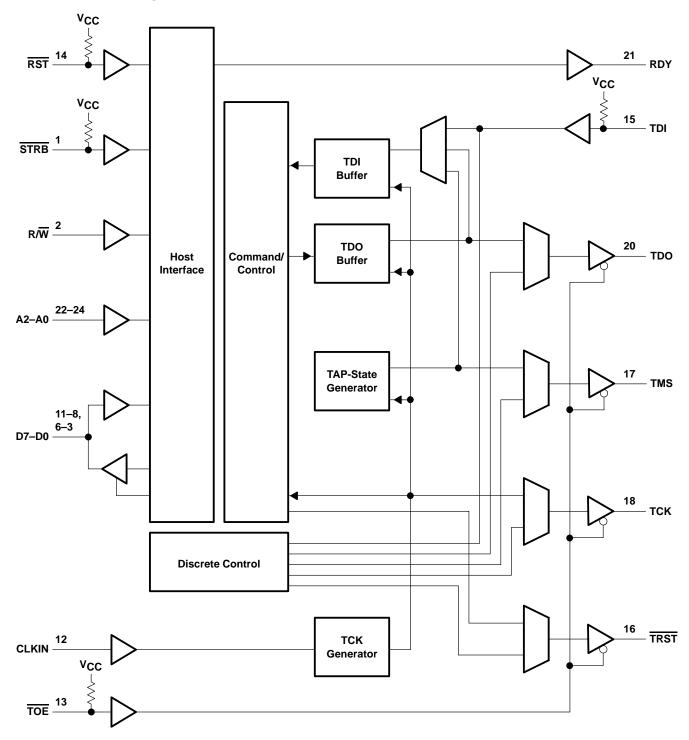

# functional block diagram

Pin numbers shown are for the DW and JT packages.

## **Terminal Functions**

| TERMINAL<br>NAME | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A2-A0            | Address inputs. A2–A0 form the 3-bit address bus that interfaces the eTBC to its microprocessor/microcontroller host. These inputs directly index the eTBC register to be accessed (read from or written to).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CLKIN            | Clock input. CLKIN is the system clock input for the eTBC. Most operations of the eTBC are synchronous to CLKIN. Internally, the CLKIN signal is divided by a programmable divisor to generate TCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| D7-D0            | Data inputs/outputs. D7–D0 form the 8-bit bidirectional data bus that interfaces the eTBC to its microprocessor/microcontroller host. Data in the eTBC registers is accessed (read or written) using this data bus. D7 is considered the most-significant bit, while D0 is considered the least-significant bit.                                                                                                                                                                                                                                                                                                                                                                                                              |

| GND              | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RDY              | Ready output. RDY is used to indicate to the microprocessor/microcontroller host whether or not the eTBC is ready to service the access (read or write) operation that is currently being requested. If RDY remains high following the initiation of an access cycle (STRB negative edge) then the eTBC is ready. Otherwise, if RDY goes low following the initiation of an access cycle (STRB negative edge) then the eTBC is not ready. In cases where the eTBC is not ready, subsequent processing in the eTBC may clear the not-ready state, which allows RDY to return high before the end of the access cycle. In any event, the RDY output returns high upon the termination of any access cycle (STRB positive edge). |

| RST              | Reset input. RST is used to initiate asynchronous reset of the eTBC. Assertion (low) of RST places the eTBC in a reset state from which it does not exit until RST is released (high). While RST is low, the eTBC ignores host writes, the RDY, TDO, TMS, and TRST outputs are high, while TCK outputs CLKIN/16. An internal pullup forces RST to a high level if it has no external connection.                                                                                                                                                                                                                                                                                                                              |

| R/W              | Read/write select. R/W is used by the microprocessor/microcontroller host to instruct the eTBC as to whether it is to perform read access (R/W high) or write access (R/W low). While R/W is high and STRB is low, the D7-D0 outputs are enabled to drive low and/or high logic levels onto the host data bus. Otherwise, while R/W is low, the D7-D0 outputs are disabled to a high-impedance state so that the host data bus can drive to the eTBC.                                                                                                                                                                                                                                                                         |

| STRB             | Read/write strobe. STRB is used by the microprocessor/microcontroller host to instruct the eTBC to initiate (STRB negative edge) or terminate/conclude (STRB positive edge) an access (read or write) operation. An internal pullup forces STRB to a high level if it has no external connection.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TCK              | Test clock. TCK transmits the TCK signal required by the eTBC's IEEE Std 1149.1 target(s). All operations of the TAP are synchronous to TCK. Generally, the TCK signal is generated internally by the eTBC by division of CLKIN by a programmable divisor. Alternatively, when the eTBC is in its discrete-control mode, a rising edge of TCK is generated on a read to the discrete-control register, while a falling edge is generated on a write to the discrete-control register.                                                                                                                                                                                                                                         |

| TDI              | Test data input. TDI receives the TDI signal output by the eTBC's IEEE Std 1149.1 target(s). It is the serial input for shifting test data from the target(s); it is sampled on the rising edge of TCK and is expected to be transferred from the target(s) on the falling edge of TCK. An internal pullup forces TDI to a high level if it has no external connection.                                                                                                                                                                                                                                                                                                                                                       |

| TDO              | Test data output. TDO transmits the TDO signal required by the eTBC's IEEE Std 1149.1 target(s). It is the serial output for shifting test data to the target(s); it is transferred on the falling edge of TCK and is sampled in the target on the rising edge of TCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| TMS              | Test mode select. TMS transmits the TMS signal required by the eTBC's IEEE Std 1149.1 target(s). It is the one control signal that directs the next TAP-controller state of the target(s). It is transferred from the eTBC on the falling edge of TCK and is sampled in the target(s) on the rising edge of TCK.                                                                                                                                                                                                                                                                                                                                                                                                              |

| TOE              | Test-output enable. TOE is the active-low output enable for the eTBC TAP outputs (TCK, TDO, TMS, TRST). When TOE is inactive (high) the TAP outputs are disabled to a high-impedance state. Otherwise, when TOE is active (low), the TAP outputs are enabled to drive low and/or high logic levels according to other eTBC functions. An internal pullup forces TOE to a high level if it has no external connection.                                                                                                                                                                                                                                                                                                         |

| TRST             | Test reset. TRST transmits the TRST signal that may be required by some of the eTBC's IEEE Std 1149.1 target(s). A low signal at TRST is intended to initiate asynchronous test reset of the connected target(s). Such a low signal at TRST is generated only when the microprocessor/microcontroller host writes an appropriate value into the eTBC command register or, while the eTBC is in discrete-control mode, into the discrete-control register.                                                                                                                                                                                                                                                                     |

| VCC              | Supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

# IEEE STD 1149.1 (JTAG) TAP MASTERS WITH 8-BIT GENERIC HOST INTERFACES

SCBS676C - DECEMBER 1996 - REVISED AUGUST 1997

# application information

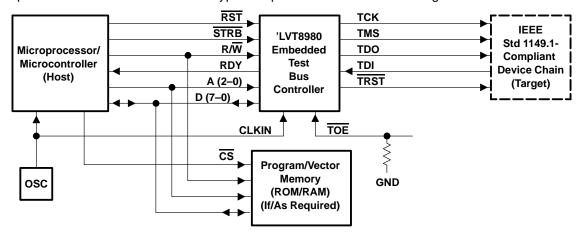

In application, the eTBC is used to master a single IEEE Std 1149.1 TAP under the control of a microprocessor/microcontroller host. A typical implementation is shown in Figure 1.

Figure 1. eTBC Application

All signals required to master IEEE Std 1149.1-compliant devices — TCK, TMS, TDO, TDI — are sourced/received by the eTBC. The eTBC can also source the optional TRST signal. Additionally, the eTBC implements high-drive output buffers, allowing it to interface directly to on- or off-board targets without need for buffering or other additional logic.

The eTBC's generic host interface allows it to act as a simple 8-bit memory- or I/O-mapped peripheral. As shown in Figure 1, for many choices of host microprocessor/microcontroller, this interface can be accomplished without additional logic. While the eTBC requires a clock input (CLKIN), in many cases it can be driven from the same source that provides a clock signal to the host.

Thus, in combination with the host microprocessor/microcontroller, the eTBC can be used to implement a two-chip embedded test-control function supporting board- and system-level built-in test based on structured IEEE Std 1149.1 test access. In some cases, for additional program and/or test vector storage, an external ROM/RAM may be required.

By use of the eTBC in such an embedded test control function, the host microprocessor/microcontroller is freed from the burden of generating the TAP-state sequences, serializing the outgoing bit stream, and deserializing the incoming bit stream. All such tasks are implemented in the eTBC, allowing the host to operate at full 8-bit parallel efficiency, host software to operate at the level of discrete scan operations versus the level of TAP manipulation, and test throughput to be maximized. The eTBC's full suite of data-scan and instruction-scan commands ensure that the host software operates efficiently.

Host efficiency and flexibility is also maximized through the eTBC's fully visible status and implementation of the ready output (RDY). RDY goes inactive during a read or write access if the host-requested access cannot be performed immediately. Thus, it can be used to insert hold or wait states back to the host. When the condition blocking the access clears, the requested access completes. Additionally, all conditions that can cause such a blocking condition are continuously updated in the eTBC status and command registers. Thus, the host software can poll the eTBC status rather than implement RDY in hardware.

## application information (continued)

The eTBC also provides several capabilities that support special target application requirements. The eTBC's test-output enable allows its master function to be disabled so that another device (an external tester, for example) can control the target TAP. Where required, due to target non-compliance or sensitivity to state sequencing, discrete-control mode provides the host software with arbitrary control of TMS and TDO sequences. Also, where targets may be sensitive to leaving Shift-DR state during scan operation, gated-TCK mode allows the TCK output to be stopped, rather than cycling the target TAP state to Pause-DR state, when service to TDI buffer or TDO buffer is required.

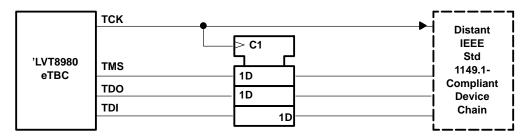

Where target devices are extremely distant (due to cabling, etc.), pipelining may be implemented at intervals along the incoming or outgoing paths to retime (deskew) the TDI, TDO, and TMS signals. An example is shown in Figure 2. In such applications, the eTBC can automatically adjust the incoming test-data bit stream to account for cycle delays introduced by the pipeline.

Figure 2. Retimed Interface to Target

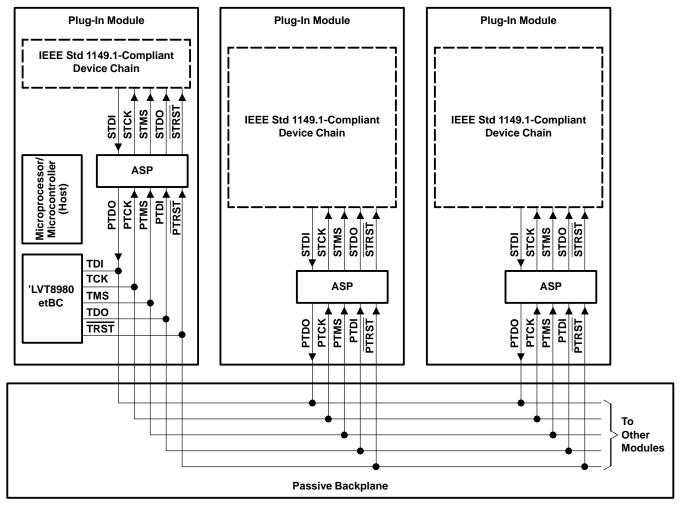

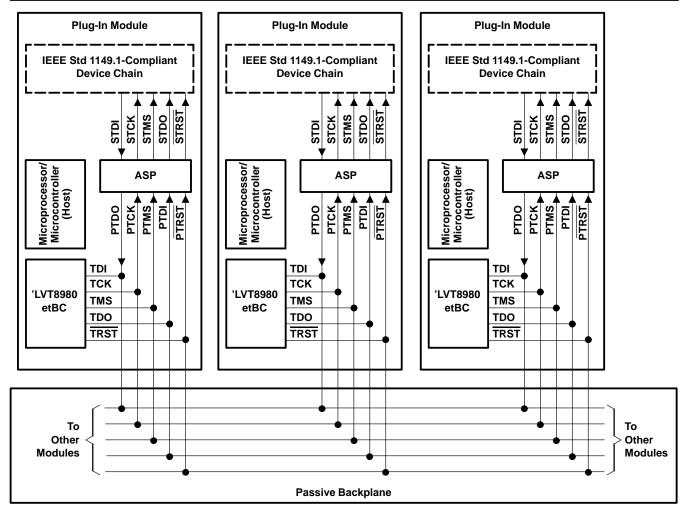

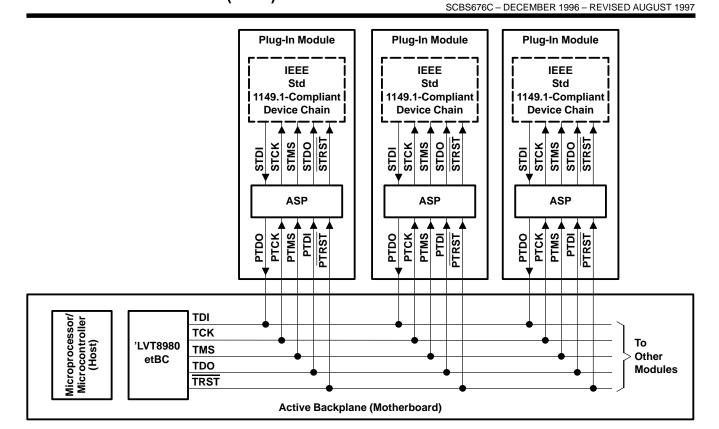

Also, in gated-TCK mode, special scan commands provide transparent support for addressable shadow protocols. Thus, in conjunction with its high-drive outputs, the eTBC can fully support multidrop backplane TAP configurations implemented with TI's addressable scan ports (ASP). Figure 3 shows a multidrop TAP configuration in a passive-backplane application implemented with a centralized (one eTBC per chassis/rack) test-control architecture, while Figure 4 shows a passive-backplane application implemented with a distributed (eTBC per module) test-control architecture. Figure 5 shows a multidrop TAP configuration in an active-backplane (motherboard) application.

Figure 3. Passive-Backplane Application With Centralized (eTBC Per Chassis) Test-Control Architecture

# IEEE STD 1149.1 (JTAG) TAP MASTERS WITH 8-BIT GENERIC HOST INTERFACES SCBS676C - DECEMBER 1996 - REVISED AUGUST 1997

Figure 4. Passive-Backplane Application With Distributed Test-Control (eTBC Per Card) Architecture

# IEEE STD 1149.1 (JTAG) TAP MASTERS WITH 8-BIT GENERIC HOST INTERFACES

Figure 5. Active-Backplane (Motherboard) Application

#### architecture

Conceptually, the eTBC can be viewed as an IEEE Std 1149.1 coprocessor/accelerator that operates in conjunction with (and under the control of) a host microprocessor/microcontroller. The eTBC implements this function using an 8-bit generic host interface and a scan-test-based command/control architecture. As shown in the functional block diagram, beyond these fundamental elements and another central block supporting discrete-control mode, the eTBC functions are accomplished in four additional blocks – one for each of the required TAP signals – a TCK generator, a TAP-state (TMS) generator, a TDO buffer, and a TDI buffer.

## host interface

The eTBC host interface is implemented generically on an 8-bit read/write data bus (D7–D0). Three address pins (A2–A0) directly index the eTBC's eight read/write registers: configurationA, configurationB, status, command, TDO buffer, TDI buffer, counter, and discrete control. The register address map is given in Table 1.

#### host access timing

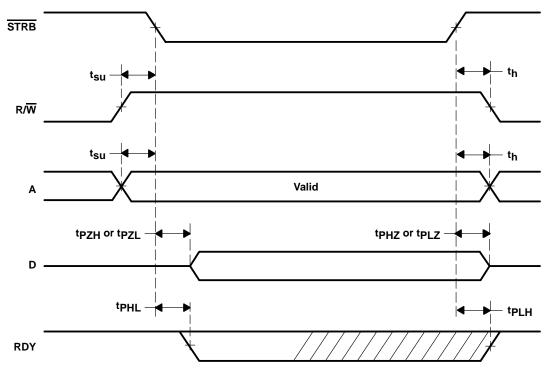

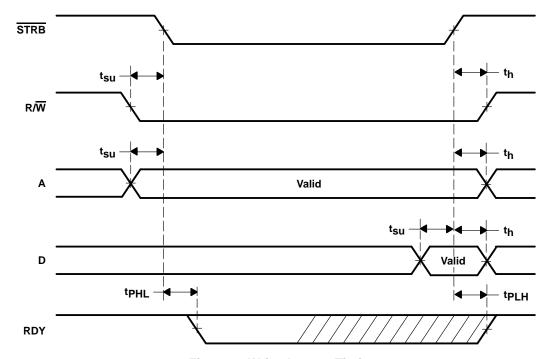

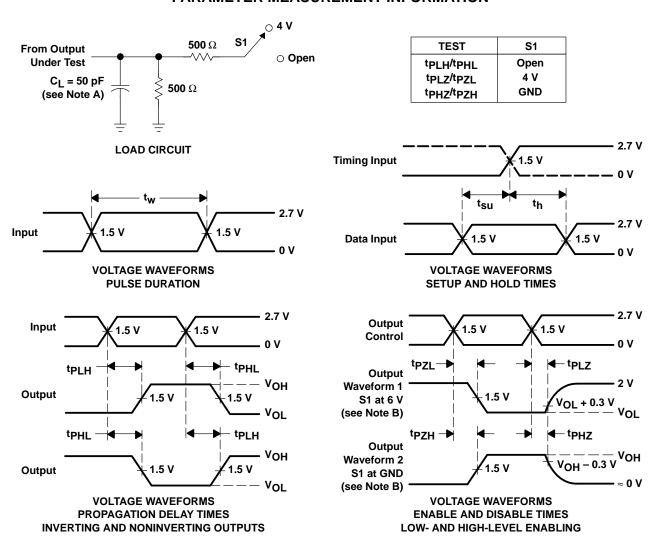

Host access timing is asynchronous to the clock input (CLKIN) and is fully controlled by the read/write strobe ( $\overline{STRB}$ ). The read/write select ( $R/\overline{W}$ ) serves to control the direction of data flow on the bidirectional data bus. Figure 6 shows the read access timing while Figure 7 shows the write access timing. As shown, for either read or write access,  $R/\overline{W}$  and address signals should be held while  $\overline{STRB}$  is low.

For read access (R/W high) the eTBC data bus outputs are made active, on the falling edge of STRB, to drive the data contained in the selected eTBC register. Otherwise, when STRB is high, the eTBC data outputs are at high impedance. Therefore, in many applications, the R/W signal can be shared in common with other host peripherals (ROM or RAM, for example) while the STRB signal is generated separately (by discrete chip-select signals available from the host or a decode logic) for each required peripheral.

## host access timing (continued)

For write access (R/W low), the eTBC data outputs remain at high impedance independent of STRB. The address of the register to be written is latched from the address pins on the falling edge of STRB, while the data to be written is latched from the data bus on the rising edge of STRB.

Figure 6. Read Access Timing

Figure 7. Write Access Timing

SCBS676C - DECEMBER 1996 - REVISED AUGUST 1997

## ready output

The ready output (RDY) from the host interface can be used, where the selected microprocessor/microcontroller supports it, to insert wait or hold states back to the host. If a host-requested access cannot be performed immediately, RDY goes inactive (low) during that given access. When the condition blocking the access clears, RDY goes active (high) and the eTBC grants the requested access. Alternatively, where such hardware-generated hold or wait states are not supported in the selected microprocessor/microcontroller host, the eTBC status and/or command registers can be polled to determine its readiness to grant a given read or write access.

Conditions that cause a host access to be blocked (and RDY to become inactive) are limited to the following:

- While the TDI buffer is empty, as indicated in status register (bit 7, TDIS), a requested read to TDI-buffer register generates RDY inactive; this condition clears, RDY goes active, and the requested access completes, when the TDI buffer is no longer empty.

- While the TDO buffer is full or is being reset upon initiation of a scan command, as indicated in status register (bit 6, TDOS), a requested write to TDO-buffer register generates RDY inactive; this condition clears, RDY goes active, and the requested access completes, when the TDO buffer is no longer full or the TDO-buffer reset completes, as applicable.

- While a command is in progress, as indicated by a non-zero value in the opcode field (bits 3–0, OPCOD) of the command register, a requested write to command, configurationA, configurationB, or counter registers generates RDY inactive. This condition clears, RDY goes active, and the requested access is complete, when the previously specified command finishes. The sole exception is the writing of a logic 1 into the software reset (bit 7, SWRST) bit of the command register, which is never blocked.

- While a full-duplex scan command is in progress, and the number of retiming-delay bits is other than zero, the number of writes to TDO-buffer register may not exceed, by more than 5, the number of reads to TDI-buffer register. A write to TDO-buffer register that does exceed this limit is blocked, and generates RDY inactive, indefinitely; the TDI-buffer register must be read before another write to TDO-buffer register.

# SN54LVT8980, SN74LVT8980 **EMBEDDED TEST-BUS CONTROLLERS** IEEE STD 1149.1 (JTAG) TAP MASTERS WITH 8-BIT GENERIC HOST INTERFACES SCBS676C - DECEMBER 1996 - REVISED AUGUST 1997

# register descriptions

A summary of the eTBC registers, their address mappings, bit assignments, reset values, and host accessibility (read/write or read-only) is provided in Table 1. All registers are fully readable by the host. All registers are fully writeable by the host with the exception of the status and TDI-buffer registers. Also, with the exception of TDO-buffer and command registers, writes to any register while a command is in progress are held off (RDY inactive) or ignored. Bits designated as reserved should be written to logic 0; read-only bits designated as reserved always read logic 0.

**Table 1. Register Summary**

| ADDRESS        | REGISTER         |                | REGISTER DETAIL (BIT ASSIGNMENTS) |       |           |       |       |       |                |       |        |

|----------------|------------------|----------------|-----------------------------------|-------|-----------|-------|-------|-------|----------------|-------|--------|

| A2-A0 REGISTER |                  | BIT 7<br>(MSB) | BIT 6                             | BIT 5 | BIT 4     | BIT 3 | BIT 2 | BIT 1 | BIT 0<br>(LSB) | VALUE | ACCESS |

| 000            | ConfigurationA   | Rese           | erved                             | NTOE  | LPBK MODE |       |       |       |                | 0x00  | R/W    |

| 001            | ConfigurationB   |                | CDIV                              |       | Reserved  |       | RD    | LY    |                | 0x80  | R/W    |

| 010            | Status           | TDIS           | TDOS                              | CTRS  | Reserved  |       | TAF   | PST   |                | 0x00  | R      |

| 011            | Command          | SWRST          | NTRST                             | EN    | IDST      |       | OPC   | OD    |                | 0x00  | R/W    |

| 100            | TDO buffer       |                |                                   |       |           |       |       |       |                | 0x00  | R/W    |

| 101            | TDI buffer       |                |                                   |       |           |       |       |       |                | 0x00  | R      |

| 110            | Counter          |                |                                   |       |           |       |       |       |                | 0x00  | R/W    |

| 111            | Discrete control |                | Res                               | erved | ·         | DNTR  | DTMS  | DTDI  | DTDO           | 0x00  | R/W    |

#### configuration registers

All eTBC test commands operate under the influence of the configurationA and configurationB registers. The decodes of the various bit groups assigned to these registers are given in Table 2 and Table 3, respectively. These registers are fully readable at all times and are fully writeable except when an eTBC command is in progress. Bit group values designated as reserved should not be written.

## **Table 2. Configuration A Register Decode**

| CONFIGU      | RATIONA |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------|---------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIT<br>GROUP | BIT NO. | VALUE   | RESULT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| NTOE         | 5       | 0       | TAP outputs (TCK, TDO, TMS, TRST) are enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| INTOE        | 5       | 1       | TAP outputs (TCK, TDO, TMS, TRST) are disabled (high impedance).                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|              |         | 00      | No loopback – TDI pin inputs to TDI buffer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| LPBK         | 4–3     | 01      | TMS loopback – TAP-state generator inputs to TDI buffer. TMS and TDO pins are fixed high.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| LFBR         | 4–3     | 10      | TDO loopback – TDO buffer inputs to TDI buffer. TMS and TDO pins are fixed high.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|              |         | 11      | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|              |         | 000     | Automatic/free-running-TCK mode – all TAP outputs are generated autonomously in the eTBC according to the active command. The TCK output runs continuously; while operating a scan command, if the TDI buffer becomes full and/or the TDO buffer becomes empty, the TAP state is cycled to Pause-DR or Pause-IR, as appropriate, until the host performs the required buffer service.                                                                                                                               |

| MODE         | 2–0     | 001     | Automatic/gated-TCK mode – all TAP outputs are generated autonomously in the eTBC according to the active command. The TCK output is run only when required to move TAP state or to progress run-test or scan operations, otherwise, it is gated off (low); while operating a scan command, if the TDI buffer becomes full and/or the TDO buffer becomes empty, the TAP state remains in Shift-IR or Shift-DR, as appropriate, but the TCK output is gated off until the host performs the required buffer service. |

|              |         | 010     | Discrete-control mode – all TAP outputs are determined by contents of the discrete-control register under control of host software.                                                                                                                                                                                                                                                                                                                                                                                 |

|              |         | 011–111 | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

#### **Table 3. ConfigurationB Register Decode**

| CONFIGU      | RATIONB |               |                                                                                                                                                                                                                            |

|--------------|---------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIT<br>GROUP | BIT NO. | VALUE         | RESULT                                                                                                                                                                                                                     |

| CDIV         | 7–5     | 000–111       | TCK = $(CLKIN)/(2^{CDIV})$ ; reset value TCK = $(CLKIN)/(2^4)$ = $CLKIN/16$                                                                                                                                                |

| RDLY         | 3–0     | 0000–11<br>11 | Number of retiming delays to accommodate = RDLY; while operating a scan command, TDI sampling is delayed by a number of TCK cycles, equal to RDLY, following the generation of Shift-DR or Shift-IR state, as appropriate. |

The negated test-output-enable (NTOE) bit allows the host to disable the TAP outputs via software in a manner analogous to the hardware  $\overline{\text{TOE}}$ . The loopback (LPBK) bit group allows the selection of the source of data to be input to the TDI buffer – from the TDI pin for normal eTBC operations or, for eTBC verification purpose, from TAP-state (TMS) generator or TDO buffer. The test mode (MODE) bit group provides a choice of automatic/free-running-TCK, automatic/gated-TCK, or discrete-control modes.

The clock-divisor (CDIV) bit group allows software control of the TCK output frequency based on a division of the CLKIN input. Divisors from  $2^0$  (1) to  $2^7$  (128) are provided. The clock divisor defaults to  $2^4$  (16) on eTBC reset (power-up, hardware-initiated, or software-initiated). The retiming-delay (RDLY) bit group provides for the automatic accommodation of retiming (pipeline) delays, which can be used to deskew the TAP signals to target scan chains that are electrically distant (due to cabling delays, etc).

#### status register

The status of the eTBC is fully reported and continuously updated in the status register. The decode of the various bit groups assigned to the status register is given in Table 4.

Table 4. Status Register Decode

| STA          | TUS     |       |                                                                                                                       |

|--------------|---------|-------|-----------------------------------------------------------------------------------------------------------------------|

| BIT<br>GROUP | BIT NO. | VALUE | RESULT                                                                                                                |

| TDIS         | 7       | 0     | The TDI buffer is empty – no TDI data is available for host read.                                                     |

| TDIS         | 1       | 1     | The TDI buffer is not empty – at least one byte of TDI data is available for host read.                               |

| TDOS         | 6       | 0     | The TDO buffer is not full – at least one byte in TDO buffer is available for host write.                             |

| 1003         | O       | 1     | The TDO buffer is full – no bytes in TDO buffer are available for host write.                                         |

| CTRS         | 5       | 0     | The counter is not loaded with a complete 32-bit value – command operation cannot begin until counter load completes. |

|              | ĺ       | 1     | The counter is loaded with a complete 32-bit value – command operation can begin.                                     |

|              |         | 0000  | The current target TAP state (as sent by eTBC) is Test-Logic-Reset.                                                   |

|              |         | 0001  | The current target TAP state (as sent by eTBC) is Select-DR-Scan.                                                     |

|              |         | 0010  | The current target TAP state (as sent by eTBC) is Capture-DR.                                                         |

|              |         | 0011  | The current target TAP state (as sent by eTBC) is Shift-DR.                                                           |

|              |         | 0100  | The current target TAP state (as sent by eTBC) is Exit1-DR.                                                           |

|              |         | 0101  | The current target TAP state (as sent by eTBC) is Pause-DR.                                                           |

|              |         | 0110  | The current target TAP state (as sent by eTBC) is Exit2-DR.                                                           |

| TAPST        | 3–0     | 0111  | The current target TAP state (as sent by eTBC) is Update-DR.                                                          |

| I IAI SI     | 3-0     | 1000  | The current target TAP state (as sent by eTBC) is Run-Test/Idle.                                                      |

|              |         | 1001  | The current target TAP state (as sent by eTBC) is Select-IR-Scan.                                                     |

|              |         | 1010  | The current target TAP state (as sent by eTBC) is Capture-IR.                                                         |

|              |         | 1011  | The current target TAP state (as sent by eTBC) is Shift-IR                                                            |

|              |         | 1100  | The current target TAP state (as sent by eTBC) is Exit1-IR.                                                           |

|              |         | 1101  | The current target TAP state (as sent by eTBC) is Pause-IR.                                                           |

|              |         | 1110  | The current target TAP state (as sent by eTBC) is Exit2-IR.                                                           |

|              |         | 1111  | The current target TAP state (as sent by eTBC) is Update-IR.                                                          |

The TDI-buffer-status (TDIS) bit reports the readiness of the TDI buffer to respond to a host read. The TDO-buffer-status (TDOS) bit reports the readiness of the TDO buffer to respond to a host write. The counter-status (CTRS) bit reports the readiness of the counter to support a command that uses the counter. The current-TAP-state (TAPST) bit group continuously reports the target TAP state as monitored by the eTBC.

#### command register

The command register is used to perform software reset of the eTBC, to discretely control the state of the TRST output when not in discrete-control mode, and to initiate test operations in the target(s). The decode of the various bits assigned to the command register is given in Table 5.

Any read to the command register while a command is in progress returns the value written to the command register upon initiation of the command. Once a command finishes, the operation-code (OPCOD) bit group in the command register is reset to null. In this way, the status of a requested command can be monitored/polled by the host.

With the exception of the software-reset (SWRST) bit, which can be written at any time, writes to the command register while a command is in progress causes RDY inactive and is ignored if the write cycle is terminated before the previously requested command finishes.

**Table 5. Command Register Decode**

| СОММ         | AND        |       |                                                          | TEST                 | OPERATION       | COMMENT               | S                     |

|--------------|------------|-------|----------------------------------------------------------|----------------------|-----------------|-----------------------|-----------------------|

| BIT<br>GROUP | BIT<br>NO. | VALUE | RESULT                                                   | WORKING<br>TAP STATE | USES<br>COUNTER | USES<br>TDI<br>BUFFER | USES<br>TDO<br>BUFFER |

| SWRST        | 7          | 0     | Normal operation                                         |                      |                 |                       |                       |

| SWKSI        | ,          | 1     | Full reset                                               | ]                    |                 |                       |                       |

| TRST         | 6          | 0     | If not in discrete-control mode, output high to TRST pin | ]                    |                 |                       |                       |

| IKSI         | b          | 1     | If not in discrete-control mode, output low to TRST pin  | ]                    |                 |                       |                       |

|              |            | 00    | Finish command in TAP state Test-Logic-Reset             | ]                    |                 |                       |                       |

| ENDST        | 5–4        | 01    | Finish command in TAP state Run-Test/Idle                | ]                    |                 |                       |                       |

| LINDST       | 5-4        | 10    | Finish command in TAP state Pause-DR                     |                      |                 |                       |                       |

|              |            | 11    | Finish command in TAP state Pause-IR                     |                      |                 |                       |                       |

|              |            | 0000  | Null                                                     |                      |                 |                       |                       |

|              |            | 0001  | Reserved                                                 |                      |                 |                       |                       |

|              |            | 0010  | Execute run test                                         | Run-Test/Idle        | Yes             | No                    | No                    |

|              |            | 0011  | Execute input-only ASP scan                              | N/A                  | Yes             | Yes                   | No                    |

|              |            | 0100  | Execute ASP scan                                         | N/A                  | Yes             | Yes                   | Yes                   |

|              |            | 0101  | Execute output-only ASP scan                             | N/A                  | Yes             | No                    | Yes                   |

|              |            | 0110  | Execute state move                                       | N/A                  | No              | No                    | No                    |

| OPCOD        | 3–0        | 0111  | Execute state jump                                       | N/A                  | No              | No                    | No                    |

| OLCOD        | 3-0        | 1000  | Execute instruction-register scan                        | Shift-IR             | Yes             | Yes                   | Yes                   |

|              |            | 1001  | Execute data-register scan                               | Shift-DR             | Yes             | Yes                   | Yes                   |

|              |            | 1010  | Execute input-only instruction-register scan             | Shift-IR             | Yes             | Yes                   | No                    |

|              |            | 1011  | Execute input-only data-register scan                    | Shift-DR             | Yes             | Yes                   | No                    |

|              |            | 1100  | Execute output-only instruction-register scan            | Shift-IR             | Yes             | No                    | Yes                   |

|              |            | 1101  | Execute output-only data-register scan                   | Shift-DR             | Yes             | No                    | Yes                   |

|              |            | 1110  | Execute recirculate instruction-register scan            | Shift-IR             | Yes             | Yes                   | No                    |

|              |            | 1111  | Execute recirculate data-register scan                   | Shift-DR             | Yes             | Yes                   | No                    |

The software-reset (SWRST) bit is provided to allow software initiation of full eTBC reset. This bit of the command register can be written at any time, regardless of the configuration or command in progress. The test-reset (TRST) bit allows direct software control of the state of  $\overline{\text{TRST}}$  output in modes other than discrete control.

The end-TAP-state (ENDST) bit group determines the TAP state in which the target scan chain is left when the requested command finishes. The operation-code (OPCOD) bit group determines the test operation to be executed in the target.

SCBS676C - DECEMBER 1996 - REVISED AUGUST 1997

#### counter register

The counter register, while only 8 bits wide like any other eTBC register, provides read/write access to the full 32-bit eTBC counter. Writes to the counter register are accomplished by four complete host access cycles, otherwise the counter is considered unloaded (CTRS = 0). Reads to the counter register likewise are accomplished by four complete host access cycles. However, reads do not affect the counter-loaded status (CTRS). The counter access (both read and write) is in least-significant-byte-first order. Any writes to the counter register while a command is in progress are ignored. The 32-bit value present in the counter at initiation of a command is used to determine the number of TCK cycles or scan bits for which the command is operated.

## TDO-buffer register

The TDO-buffer register, while only 8 bits wide like any other eTBC register, provides write access to the full  $4 \times 8$  (32-bit) FIFO that comprises the TDO buffer. The TDO-buffer register can be written as long as the TDO buffer does not become full. When the TDO buffer becomes full, further writes to the TDO-buffer register cause RDY inactive (and consequent hold or wait states to be sent back to the host, if supported) and cause the write to be ignored if the write cycle is terminated before the TDO-buffer-full status is cleared.

## TDI-buffer register

The TDI-buffer register, while only 8 bits wide like any other eTBC register, provides read access to the full  $4 \times 8$ (32-bit) FIFO that comprises the TDI buffer. The TDI-buffer register can be read as long as the TDI buffer does not become empty. When the TDI buffer becomes empty, further reads to the TDI-buffer register cause RDY inactive (and consequent hold or wait states to be sent back to the host, if supported) and cause the read data to be invalid if the read cycle is terminated before the TDI-buffer-empty status is cleared.

## discrete-control register

The discrete-control register is used to program the state of the TAP outputs (TCK, TDO, TMS, TRST) and to poll the state of the TAP input (TDI) when the eTBC is in its discrete-control mode. The contents of the discrete-control register determine values output to TDO, TMS, and TRST according to the decode in Table 6. The TCK output is generated on each read and write to the discrete-control register; writes generate TCK falling edge, while reads generate TCK rising edge. In modes other than the discrete-control mode, this register is fully writeable and readable, but writes and reads have no effect on eTBC or target operation.

Table 6. Discrete-Control Register Decode

| DISCRETE C | ONTROL  | VALUE | RESULT                                                                  |

|------------|---------|-------|-------------------------------------------------------------------------|

| BIT GROUP  | BIT NO. | VALUE | RESULI                                                                  |

| DNTR       | 3       | 0     | If in discrete-control mode, output low to TRST pin, otherwise nothing  |

| DNTK       | 3       | 1     | If in discrete-control mode, output high to TRST pin, otherwise nothing |

| DTMS       | 2       | 0     | If in discrete-control mode, output low to TMS pin, otherwise nothing   |

| DTIVIS     | 2       | 1     | If in discrete-control mode, output high to TMS pin, otherwise nothing  |

| DTDI       | 1       | 0     | The TDI data received is a logic 0.                                     |

| DIDI       |         | 1     | The TDI data received is a logic 1.                                     |

| DTDO       | 0       | 0     | If in discrete-control mode, output low to TDO pin, otherwise nothing   |

| סטוט       | J       | 1     | If in discrete-control mode, output high to TDO pin, otherwise nothing  |

# IEEE STD 1149.1 (JTAG) TAP MASTERS WITH 8-BIT GENERIC HOST INTERFACES

#### command/control

The eTBC's command-based architecture is structured around a set of comprehensive IEEE Std 1149.1 (JTAG) test objectives, which include TAP state movement, scan operations, and run test (operation of test logic in Run-Test/Idle state). The set of test operations, as decoded from the command register (bits 3–0, OPCOD) is given in Table 5. Commands are initiated by writing the eTBC command register; upon command initiation, the test-control logic is initialized and the TDO and TDI buffers are cleared. Command completion is indicated when the operation code (OPCOD) field of the command register returns to the value of the null command.

The eTBC command operation is modified by the configurationA, and configurationB registers, which should be written prior to writing the command register, as the values in these registers cannot be modified while a command is in progress. Also, commands are only operated in automatic test modes, as specified in the configurationA register (bits 2–0, MODE) – while in the discrete-control mode, commands are ignored.

All eTBC commands operate similarly to accomplish IEEE Std 1149.1 test objectives. First, the eTBC generates a TMS sequence to move the target scan chain from its current TAP state to a working state that depends on the test objective. Second, the command is operated (test run, bits scanned) in the working state for a number of TCK cycles (or scan bits) determined by the value of the counter upon command initiation. Third, the eTBC generates a TMS sequence to move the target scan chain from the working state to the end state specified in the command register (bits 5–4, ENDST). For some commands, one or more of these steps are omitted.

#### TAP-state-movement commands

Two eTBC commands are provided to accomplish TAP state movement. The state-move command operates to generate a TMS sequence to move the target scan chain directly from its current TAP state to the end state specified in the command register. The state-jump command moves the eTBC's stored value of the target TAP state without generating any changes to the TMS output. The state-jump command can therefore be used to switch between targets that share the same test bus, such as those in a multidrop backplane configuration implemented with TI addressable scan ports, but that may be left in different TAP states.

#### run-test command

The run-test command allows the test logic of the target scan chain to execute autonomously in the Run-Test/Idle TAP state. Such test logic is commonly used to implement chip- or board-level built-in self test. The run-test command generates TMS sequences to move the target scan chain from its current TAP state to the Run-Test/Idle TAP state where it remains for a number of TCK cycles determined by the value of the counter upon command initiation. Upon the countdown of the counter to zero, the eTBC generates TMS sequences to move the target scan chain to the end state specified in the command register.

#### scan commands

Eleven eTBC commands are provided to perform scan operations to target scan chains. These can be classified by the destination of scan data in the target – addressable scan port (ASP), IEEE Std 1149.1 instruction register, or IEEE Std 1149.1 data register – and by the nature/direction of the data transfer – full-duplex (default), input-only, output-only, or recirculate. The only combination of these two factors that is not implemented is recirculate ASP scan.

## addressable scan port (ASP) scan commands

The ASP scan commands scan data to and/or from an addressable scan port target. Since ASP devices require that TMS remain fixed throughout their select and acknowledge protocols, the eTBC does not generate TMS sequences or change its stored value of the target's TAP state. Also, for the same reason, ASP scan commands that target ASP devices should be operated in gated-TCK mode. The ASP scan commands do allow data written to the TDO buffer to be driven serially onto the TDO pin and bits received serially at the TDI pin to be stored into the TDI buffer for reading by the host. However, the ASP scan commands do not perform any bit-pair encoding of ASP select protocols or decoding of ASP acknowledge protocols. Such encoding/decoding must be performed in the host. The number of data bits transferred in and/or out is determined by the value of the counter upon command initiation.

SCBS676C - DECEMBER 1996 - REVISED AUGUST 1997

## instruction-register scan commands

The instruction-register scan commands scan bits to and/or from the concatenation of instruction registers in a target scan chain. The eTBC generates a TMS sequence to move the target scan chain from its current TAP state to the Shift-IR TAP state. Data written to the TDO buffer can be driven serially onto the TDO pin and bits received serially at the TDI pin can be stored into the TDI buffer for reading by the host. The number of data bits transferred in and/or out is determined by the value of the counter upon command initiation. If, during the operation of an instruction register scan command, the TDO buffer becomes empty, or the TDI buffer becomes full, the TAP state is sequenced to Pause-IR (if in free-running-TCK mode) or the TCK output is gated off (if in gated-TCK mode) until the required buffer service is performed. Upon the countdown of the counter to zero, the eTBC generates TMS sequences to move the target scan chain to the end state specified in the command register.

## data-register scan commands

The data-register scan commands operate to scan bits to and/or from the concatenation of data registers in a target scan chain. The eTBC generates a TMS sequence to move the target scan chain from its current TAP state to the Shift-DR TAP state. Data written to the TDO buffer may be driven serially onto the TDO pin and bits received serially at the TDI pin may be stored into the TDI buffer for reading by the host. The number of data bits transferred in and/or out is determined by the value of the counter upon command initiation. If, during the operation of a data-register scan command, the TDO buffer becomes empty, or the TDI buffer becomes full, the TAP state is sequenced to Pause-DR (if in free-running-TCK mode) or the TCK output is gated off (if in gated-TCK mode) until the required buffer service is performed. Upon the countdown of the counter to zero, the eTBC generates TMS sequences to move the target scan chain to the end state specified in the command register.

#### other scan-command variations

As noted before, the nature/direction of the data transfer for any scan command can vary along with the destination of scan data in the target, as follows:

- For scan commands of the full-duplex (default) class, both TDO buffer and TDI buffer are used to scan data to and from the target scan chain, respectively.

- For scan commands of the input-only class, only the TDI buffer is used to scan data from the target scan chain; outgoing TDO data is fixed at a high level throughout the scan operation.

- For scan commands of the output-only class, only the TDO buffer is used to scan data to the target scan chain; incoming TDI data is simply ignored.

- For scan commands of the recirculate class, only the TDI buffer is used to scan data from the target scan chain; outgoing TDO data is generated by recirculating the incoming TDI data back into the target scan chain.

#### counter

As described above, the value loaded in the eTBC's 32-bit counter at initiation of a command is used to specify the number of TCK cycles or scan bits to remain in the command's working state. As each TCK cycle or scan bit is processed for a run-test or scan command, respectively, the counter value is decremented. When the counter value reaches zero, the command leaves its working state to finish in the end state specified in the command register.

Before a command that uses the counter can be initiated, a full 32-bit value should be loaded by four consecutive writes to the counter register. As well, the full 32-bit current value of the counter can be observed by four consecutive reads to the counter register. The counter status (unloaded/loaded) is maintained and observable in the status register (bit 5, CTRS).

Upon eTBC reset (power-up, hardware-initiated, or software-initiated), the counter is cleared and assumes its unloaded state.

# SN54LVT8980, SN74LVT8980 EMBEDDED TEST-BUS CONTROLLERS

# IEEE STD 1149.1 (JTAG) TAP MASTERS WITH 8-BIT GENERIC HOST INTERFACES SCBS676C - DECEMBER 1996 - REVISED AUGUST 1997

## TCK generator

The TCK generator sources the test clock (TCK) signal required by the IEEE Std 1149.1 target(s) and the eTBC-internal test-control logic. The fundamental TCK frequency is produced by division of CLKIN. The divisor is programmable within a range of 1 to 128 in the configurationB register (bits 7–5, CDIV). The TCK output to the target(s) operate in free-running or gated modes. The free-running mode toggles TCK continuously, based on CLKIN, while the gated mode operates the TCK only when required to move the target TAP state or to perform a run-test or scan operation.

While the eTBC is in discrete-control mode, the TCK generator is not used; instead, the state of TCK is toggled on each alternating read and write to the discrete-control register. A falling edge of TCK is produced by write, while a rising edge of TCK is produced by read.

Upon eTBC reset (power-up, hardware-initiated, or software-initiated), the TCK generator assumes its free-running mode with a clock divisor of 16 (TCK = CLKIN/16).

## **TAP-state generator**

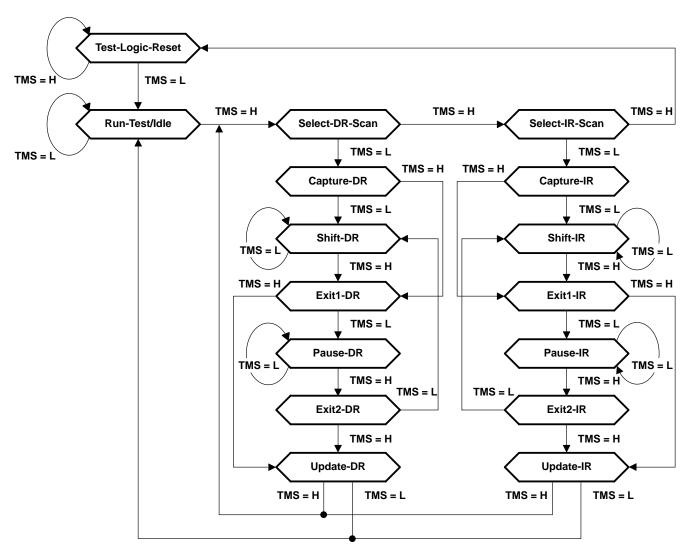

The TAP-state generator sources the TMS signal, which sequences the TAP controllers of connected IEEE Std 1149.1-compliant target devices. The TAP controller specified by IEEE Std 1149.1 is a synchronous finite-state machine that provides test control signals throughout each target device; its state diagram is shown in Figure 8. This diagram and the TAP-controller states are discussed subsequently.

The TAP-state generator operates under the control of an executing command to generate the TMS sequences required to move connected target devices from one stable state to another, to capture and scan test data into/out of target devices, and to operate built-in test modes of target devices in the Run-Test/Idle state.

The TAP state currently being generated is always maintained by the TAP-state generator and is constantly available in the eTBC status register (bits 3–0, TAPST) for host read. Based on the TAP state that is current upon command initiation, the TAP-state generator will source a defined sequence of TMS values to reach the TAP state in which the command is progressed (e.g., Shift-IR, Shift-DR, Run-Test/Idle), and ultimately to reach the specified end TAP state. These sequences are detailed in Tables 7–12.

While the eTBC is in free-running-TCK mode, if a currently operating scan command empties or fills a required test data buffer, then the TAP-state generator sources the TMS sequences required to move the connected target devices to their Pause-IR or Pause-DR states. In such case, the TAP-state generator maintains target devices in their Pause-IR or Pause-DR states until the required test data buffer is serviced appropriately. However, if such a buffer condition occurs while the eTBC is in gated-TCK mode, the TAP-state generator maintains the target devices in their Shift-IR or Shift-DR states while the TCK is gated off.

While the eTBC is in discrete-control mode, the TAP-state generator is not used; instead, the state of the TMS pin is determined by the contents of the discrete-control register. Thus, TMS sequences that cannot be generated automatically still can be applied through the eTBC to targets that require such (e.g., near-compliant devices).

The TAP-state generator also is not used during the operation of the special addressable shadow protocol (ASP) scan commands. Since, by definition, ASPs operate only while the TAP is idling (maintaining one of the TAP states Test-Logic-Reset, Run-Test/Idle, Pause-IR, or Pause-DR), the TMS pin must be maintained at the value it held upon initiation of the ASP scan command.

For eTBC verification/debugging, in addition to continuous update of the current target TAP state in the eTBC status register, the output of the TAP-state (TMS) generator can be selected for loopback into the TDI buffer. When this TMS-loopback mode is selected, although a host-requested command executes in the eTBC, the target is not affected, as both TMS and TDI are fixed at a high level.

Upon eTBC reset (power up, hardware initiated, or software initiated), the TAP-state generator assumes the Test-Logic-Reset TAP state.

# SN54LVT8980, SN74LVT8980 **EMBEDDED TEST-BUS CONTROLLERS**

# IEEE STD 1149.1 (JTAG) TAP MASTERS WITH 8-BIT GENERIC HOST INTERFACES SCBS676C - DECEMBER 1996 - REVISED AUGUST 1997

## Table 7. TMS Sequencing From TAP State Test-Logic-Reset

|             | FROM TEST-LOGIC-RESET (TMS = H) TO: |             |                      |             |                      |             |                      |             |                      |             |                      |  |  |

|-------------|-------------------------------------|-------------|----------------------|-------------|----------------------|-------------|----------------------|-------------|----------------------|-------------|----------------------|--|--|

| TEST-L      | TEST-LOGIC-RESET RUN-TEST-IDLE      |             | EST-IDLE             | SI          | HFT-DR               | PAUSE-DR    |                      | SHIFT-IR    |                      | PAUSE-IR    |                      |  |  |

| NEXT<br>TMS | NEXT<br>TAP<br>STATE                | NEXT<br>TMS | NEXT<br>TAP<br>STATE | NEXT<br>TMS | NEXT<br>TAP<br>STATE | NEXT<br>TMS | NEXT<br>TAP<br>STATE | NEXT<br>TMS | NEXT<br>TAP<br>STATE | NEXT<br>TMS | NEXT<br>TAP<br>STATE |  |  |

| Н           | T-L-R                               | L           | R-T/I                |  |  |

|             |                                     |             |                      | Н           | S-DR-S               | Н           | S-DR-S               | Н           | S-DR-S               | Н           | S-DR-S               |  |  |

|             |                                     |             |                      | L           | Capture-DR           | L           | Capture-DR           | Н           | S-IR-S               | Н           | S-IR-S               |  |  |

|             |                                     |             |                      | L           | Shift-DR             | Н           | Exit1-DR             | L           | Capture-IR           | L           | Capture-IR           |  |  |

|             |                                     |             |                      |             |                      | L           | Pause-DR             | L           | Shift-IR             | Н           | Exit1-IR             |  |  |

|             |                                     |             |                      |             |                      |             |                      |             |                      | L           | Pause-IR             |  |  |

## Table 8. TMS Sequencing From TAP State Run-Test/Idle

|             | FROM RUN-TEST/IDLE (TMS = L) TO: |             |                      |             |                      |             |                      |             |                      |             |                      |  |  |

|-------------|----------------------------------|-------------|----------------------|-------------|----------------------|-------------|----------------------|-------------|----------------------|-------------|----------------------|--|--|

| TEST-L      | OGIC-RESET                       | RUN-TI      | EST-IDLE             | SI          | HFT-DR               | PAUSE-DR    |                      | SHIFT-IR    |                      | PAUSE-IR    |                      |  |  |

| NEXT<br>TMS | NEXT<br>TAP<br>STATE             | NEXT<br>TMS | NEXT<br>TAP<br>STATE | NEXT<br>TMS | NEXT<br>TAP<br>STATE | NEXT<br>TMS | NEXT<br>TAP<br>STATE | NEXT<br>TMS | NEXT<br>TAP<br>STATE | NEXT<br>TMS | NEXT<br>TAP<br>STATE |  |  |

| Н           | S-DR-S                           | L           | R-T/I                | Н           | S-DR-S               | Н           | S-DR-S               | Н           | S-DR-S               | Н           | S-DR-S               |  |  |

| Н           | S-IR-S                           |             |                      | L           | Capture-DR           | L           | Capture-DR           | Н           | S-IR-S               | Н           | S-IR-S               |  |  |

| Н           | T-L-R                            |             |                      | L           | Shift-DR             | Н           | Exit1-DR             | L           | Capture-IR           | L           | Capture-IR           |  |  |

|             |                                  |             |                      |             |                      | L           | Pause-DR             | L           | Shift-IR             | Н           | Exit1-IR             |  |  |

|             | ·                                | ·           | ·                    |             |                      |             |                      |             |                      | L           | Pause-IR             |  |  |

Table 9. TMS Sequencing From TAP State Pause-DR

|             | FROM PAUSE-DR (TMS = L) TO: |             |                      |             |                      |             |                      |             |                      |             |                      |  |

|-------------|-----------------------------|-------------|----------------------|-------------|----------------------|-------------|----------------------|-------------|----------------------|-------------|----------------------|--|

| TEST-L      | OGIC-RESET                  | RUN-        | TEST-IDLE            | SH          | IIFT-DR              | PAUSE-DR    |                      | SHIFT-IR    |                      | PA          | USE-IR               |  |

| NEXT<br>TMS | NEXT<br>TAP<br>STATE        | NEXT<br>TMS | NEXT<br>TAP<br>STATE | NEXT<br>TMS | NEXT<br>TAP<br>STATE | NEXT<br>TMS | NEXT<br>TAP<br>STATE | NEXT<br>TMS | NEXT<br>TAP<br>STATE | NEXT<br>TMS | NEXT<br>TAP<br>STATE |  |

| Н           | Exit2-DR                    | Н           | Exit2-DR             | Н           | Exit2-DR             | Н           | Exit2-DR             | Н           | Exit2-DR             | Н           | Exit2-DR             |  |

| Н           | Update-DR                   | Н           | Update-DR            | L           | Shift-DR             | Н           | Update-DR            | Н           | Update-DR            | Н           | Update-DR            |  |

| Н           | S-DR-S                      | L           | R-T/I                |             |                      | Н           | S-DR-S               | Н           | S-DR-S               | Н           | S-DR-S               |  |

| Н           | S-IR-S                      |             |                      |             |                      | L           | Capture-DR           | Н           | S-IR-S               | Н           | S-IR-S               |  |

| Н           | T-L-R                       |             |                      |             |                      | Н           | Exit1-DR             | L           | Capture-IR           | L           | Capture-IR           |  |

|             |                             |             |                      |             |                      | L           | Pause-DR             | L           | Shift-IR             | Н           | Exit1-IR             |  |

|             |                             |             |                      |             |                      |             |                      |             |                      | L           | Pause-IR             |  |

# SN54LVT8980, SN74LVT8980 EMBEDDED TEST-BUS CONTROLLERS IEEE STD 1149.1 (JTAG) TAP MASTERS WITH 8-BIT GENERIC HOST INTERFACES SCBS676C - DECEMBER 1996 - REVISED AUGUST 1997

# Table 10. TMS Sequencing From TAP State Pause-IR

|             | FROM PAUSE-IR (TMS = L) TO: |             |                      |             |                      |             |                      |             |                      |             |                      |  |  |  |

|-------------|-----------------------------|-------------|----------------------|-------------|----------------------|-------------|----------------------|-------------|----------------------|-------------|----------------------|--|--|--|

| TEST-L      | OGIC-RESET                  | RUN-T       | EST-IDLE             | SI          | HFT-DR               | PAUSE-DR    |                      | SHIFT-IR    |                      | PA          | USE-IR               |  |  |  |

| NEXT<br>TMS | NEXT<br>TAP<br>STATE        | NEXT<br>TMS | NEXT<br>TAP<br>STATE | NEXT<br>TMS | NEXT<br>TAP<br>STATE | NEXT<br>TMS | NEXT<br>TAP<br>STATE | NEXT<br>TMS | NEXT<br>TAP<br>STATE | NEXT<br>TMS | NEXT<br>TAP<br>STATE |  |  |  |

| Н           | Exit2-IR                    | Н           | Exit2-IR             | Н           | Exit2-IR             | Н           | Exit2-IR             | Н           | Exit2-IR             | Н           | Exit2-IR             |  |  |  |

| Н           | Update-IR                   | Н           | Update-IR            | Н           | Update-IR            | Н           | Update-IR            | L           | Shift-IR             | Н           | Update-IR            |  |  |  |

| Н           | S-DR-S                      | L           | R-T/I                | Н           | S-DR-S               | Η           | S-DR-S               |             |                      | Н           | S-DR-S               |  |  |  |