# Rapid Energy Transfer to an Energy Buffer

CLAUDIA MUÑIZ GARCÍA

Master of Science Thesis Stockholm, Sweden 2007

COS/CCS 2007-22

Kungliga Tekniska Högskolan Royal Institute of Technology

# Rapid Energy Transfer to an Energy Buffer

Master Thesis Last revised: 2007-08-31

Claudia Muñiz García email: claudiamunizgarcia@gmail.com

Examiner

Professor Gerald Q. Maguire Jr.

Supervisor Professor Mark T. Smith

## Abstract (ENGLISH)

This master thesis introduces a new technology applicable to nearly all mobile and portable electrical devices since all of them need energy to operate. This thesis attempts to cut the last wire - this one the wire to the primary power source. In other words, fast and efficient wireless energy transference through a strong, focused near magnetic field whose fast attenuation will avoid interference with surrounding communication systems or human harm. This energy is transferred to and will be stored inside the mobile device where nothing but a small and simple secondary circuit has been placed.

The thesis project began by creating an initial SPICE computer model, providing an easy and rapid way of testing both convergence and feasibility of the topology as the design evolved from the well-known and widely used Switch Model Power Supply technology through to the detailed design and implementation of the prototype, including supporting the iterative process of testing and optimizing, all stages are carefully described in the document. The thesis shows both theoretically and practically that this idea is feasible and capable of power transmission.

## Sammanfattning

Detta examensarbete introducerar en ny teknologi som är applicerbar till de flesta mobila och portabla elektriska apparater då dessa behöver energi för att fungera. Detta arbete försöker klippa den sista ledningen den som leder till den primära kraftkällan. Med andra ord, är denna teknik en snabb och effektiv trådlös energiöverföring genom ett starkt, fokuserat närbeläget magnetfält. Tack vare magnetfältets kraftiga dämpning undviks interferens med intilliggande kommunikationssystem eller personskador. Denna energi är överförd till, och lagras inuti en bärbar apparat där endast en liten och enkel sekundärkrets har placerats.

Examensarbetsprojektet påbörjades med skapandet av en inledande SPICE datormodell. Modellen möjliggjorde ett enkelt och snabbt sätt att testa både konvergens och genomförbarhet av topologin samtidigt som designen utvecklades från den välkända och vitt använda Switch Power Supply-teknologin till den detaljerade designen och implementationen av prototypen. Modellen stöttade samtidigt den iterativa processen av test och optimering. Alla faser är utförligt beskrivna i rapporten och arbetet visar både teoretiskt och praktiskt att denna idé är genomförbar och möjliggör kraftöverföring.

# Table of Contents

| 1. Introdi       | uction                                                                                 | 1      |

|------------------|----------------------------------------------------------------------------------------|--------|

| 2. Backgr        | ound/Related Research                                                                  | 1      |

| 3. Method        | d/approach                                                                             | 4      |

|                  | configuration: Basic Parts, Functioning                                                |        |

| 3.1.1.           | V <sub>IN</sub>                                                                        |        |

| 3.1.2.           | Reservoir capacitor                                                                    |        |

| 3.1.3.<br>3.1.4. | Buck Regulator                                                                         |        |

| 3.1.4.<br>3.1.5. | Reference Voltage Regulation LoopInternal Error Amplifier                              |        |

| 3.1.5.<br>3.1.6. | Current Sensing through the Primary Arm of the Transformer                             |        |

| 3.1.7.           | IC protection against transient overcurrents                                           |        |

| 3.1.8.           | Switching frequency (f <sub>SW</sub> )                                                 |        |

| 3.1.9.           | Dead Time: Duty Cycle time decrease                                                    |        |

| _                | ology modifications: From suggested to desired implemen                                | tation |

| 4. Сотри         | ter Model of a generic SMPS                                                            | 12     |

| 4.1. Cho         | ice of Simulation Environment                                                          | 12     |

| 4.2. Sim         | ulation Approach Method                                                                | 13     |

|                  | are Implementation                                                                     |        |

| 5.1. Har         | dware Design                                                                           | 17     |

| 5.2. Har         | dware Construction                                                                     | 18     |

| 53 Har           | dware Refinements                                                                      | 20     |

|                  | nitial Tests                                                                           |        |

|                  | eedback from these initial tests, resulting design modifications                       |        |

|                  | ystem Startup                                                                          |        |

|                  | dware Tests / Data Collect                                                             |        |

|                  | xperimental designxperimental design                                                   |        |

|                  | est #1: Regulated output at the Secondary                                              |        |

|                  | est #2: τ and effective R identification                                               |        |

|                  | est #3: Energy transfer comparison with different C <sub>L</sub> values                |        |

|                  | est #4: Energy Transmission comparison with different NS                               |        |

|                  | est #5: Energy Transmission comparison with different $N_{\text{S}}$ / $V_{\text{DC}}$ |        |

| 6. Results       | 5                                                                                      | 45     |

| 6.1. SPICE Model Results                        | 45 |

|-------------------------------------------------|----|

| 6.1.1. sources.cir                              |    |

| 6.1.2. CCMPWM.cir                               |    |

|                                                 |    |

| 7. Discussion/analysis of results               |    |

| 7.1. Discussion of XSPICE Model                 | 52 |

| 7.2. Discussion of Measurements                 |    |

| 7.2.1. Misalignment of the cores                |    |

| 7.2.2. Phase opposition                         |    |

| 7.2.4. Circuit behaviour                        |    |

| 8. Conclusions and Future Work                  | 64 |

| Appendix A: Switching Mode Power Supplies       | 70 |

| A.1. Introduction                               | 70 |

| A.2. SMPS main features                         | 71 |

| A.2.1. Buck Topology                            |    |

| A.2.2. Boost TopologyA.2.3. Buck-Boost Topology |    |

| A.2.4. Final Choice                             |    |

| Appendix B: Intermediate SPICE results          | 80 |

| B.1. Introduction                               | 80 |

| B.2. First Version: Buck Regulator              | 80 |

| B.3. Second Version: SMPS with the addition     | 82 |

| B.4. Third Version: SMPS with the addition of   | 86 |

| B.5. Final Version: SMPS with the addition of   | 87 |

| B.6. sources.cir                                | 88 |

| B.7. CCMPWM.cir                                 | 88 |

| B.8. bucktestccm.cir                            | 89 |

| B.9. sec_W.cir                                  | 90 |

| B.10. ter_W.cir                                 | 91 |

| B 11 final cir                                  | 93 |

| B.12. sourcesimplemented.cir                                          | 94  |

|-----------------------------------------------------------------------|-----|

| B.13. CCMPWMimplemented.cir                                           | 94  |

| B.14. implemented.cir                                                 | 96  |

| Appendix C: Measured Data                                             | 98  |

| C.1. Values from test#5                                               | 98  |

| C.1.1. Tables from test#5.1: Card with different V <sub>DC</sub>      |     |

| C.1.2. Tables from test#5.2: 1 Washer with different V <sub>DC</sub>  |     |

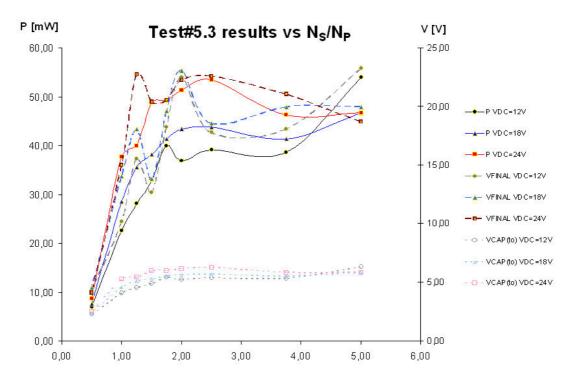

| C.1.3. Tables from test#5.3: 2 Washers with different $V_{DC}$        |     |

| C.2. Graphs from test#5                                               | 103 |

| C.2.1. Graphs from test#5.1: Card with different $V_{DC}$             |     |

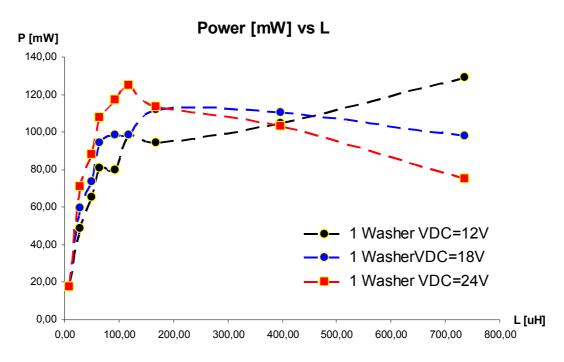

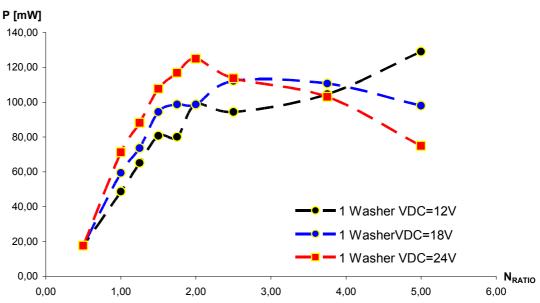

| C.2.2. Graphs from test#5.2: 1 washer with different V <sub>DC</sub>  |     |

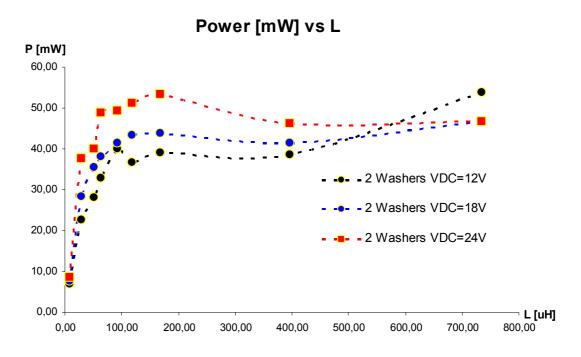

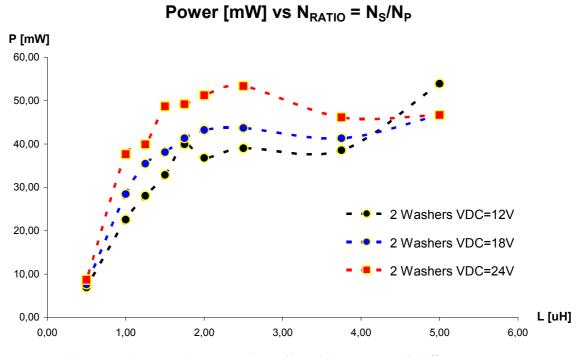

| C.2.3. Graphs from test#5.3: 2 washers with different V <sub>DC</sub> |     |

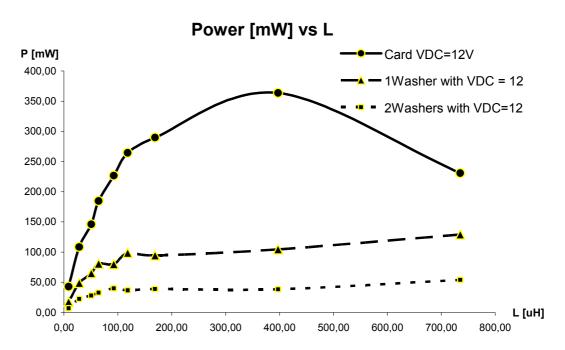

| C.2.4. Behaviour comparative with $V_{DC} = 12V$                      |     |

| C.2.5. Behaviour comparative with $V_{DC} = 18V$                      |     |

| C.2.6. Behaviour comparative with $V_{DC} = 24V$                      |     |

# Table of Figures

| Figure 1: Switching Power Conversion                                                                                              | 2  |

|-----------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2: Simple sketch of the system                                                                                             | 3  |

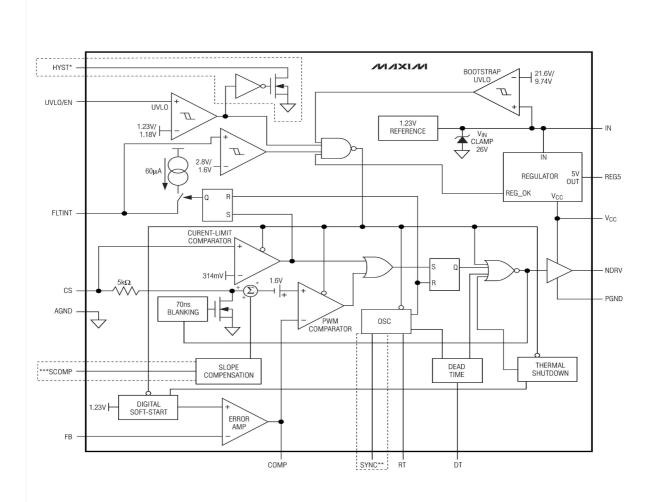

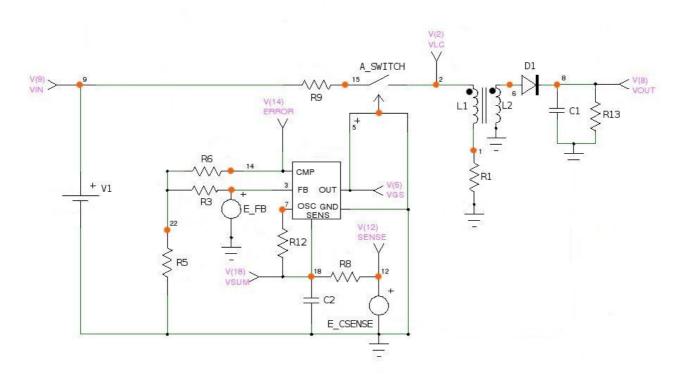

| Figure 3: MAX5068E on the initial configuration                                                                                   | 5  |

| Figure 4: UVLO/EN regulation circuit (appears here with the permission of the copyright owner)[15]                                | 6  |

| Figure 5: NDRV ON at 75% Duty Cycle (left); spikes when NDRV should be OFF (right)                                                |    |

| Figure 6: Ideal transformer behavior [16]                                                                                         |    |

| Figure 7: Capacitor charge through a RC series circuit                                                                            |    |

| Figure 8: Initial suggested configuration                                                                                         |    |

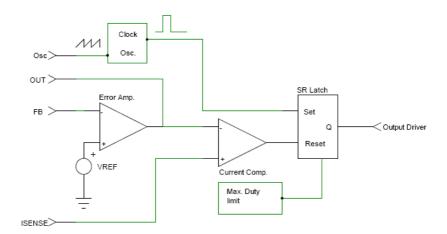

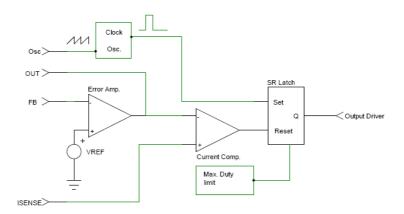

| Figure 9: The internal circuitry of a generic single output CCM PWM controller [29]                                               |    |

| Figure 10: Suggested architecture for a current-mode controlled Buck regulator (see appendix A.2.1. for more                      |    |

| information about Buck regulators) [29]                                                                                           | 14 |

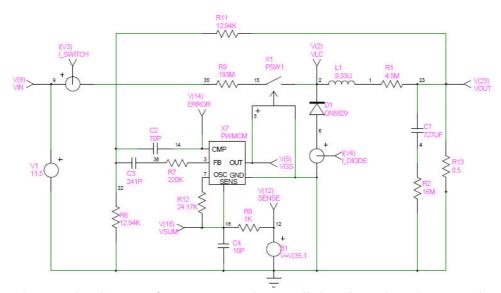

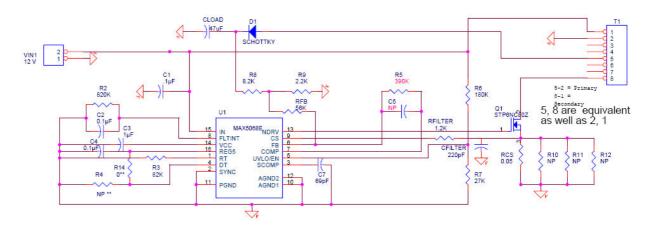

| Figure 11: Internal MAX5068 configuration (figure appears here with permission from the copyright owner)[33]                      | 15 |

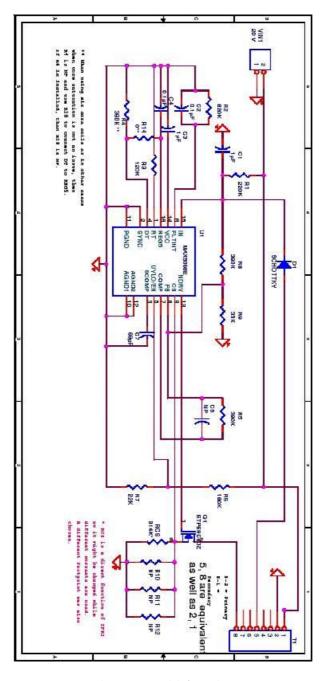

| Figure 12: Initial Design                                                                                                         |    |

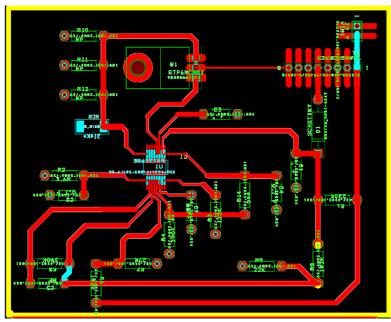

| Figure 13: PCB footprint                                                                                                          |    |

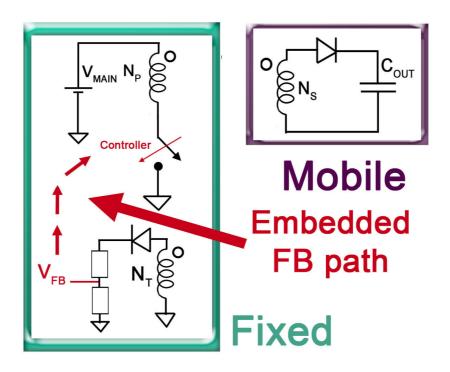

| Figure 14: New configuration for the FB path                                                                                      |    |

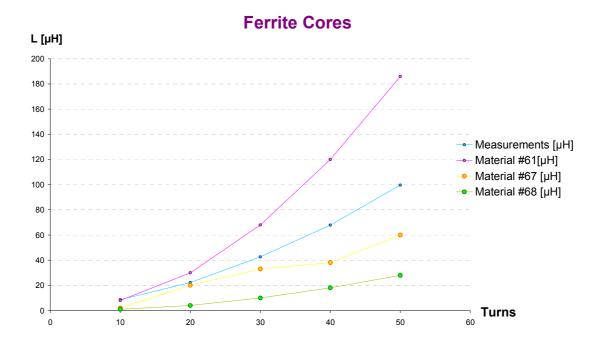

| Figure 15: Graph comparing different materials and measured core behavior                                                         |    |

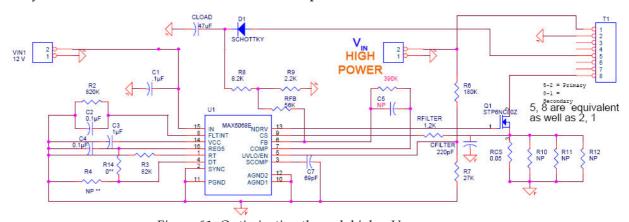

| Figure 16: Capture Schematic of the refined circuit                                                                               |    |

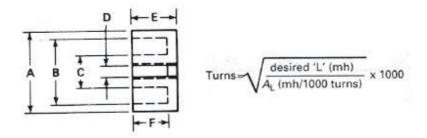

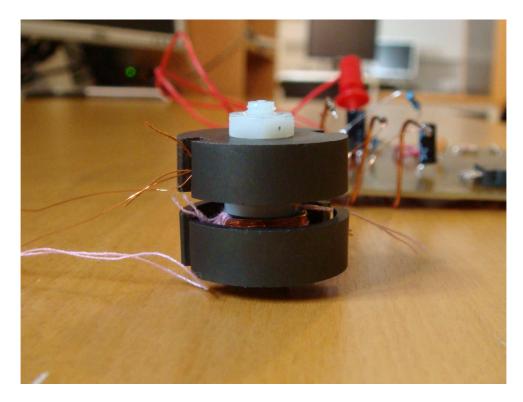

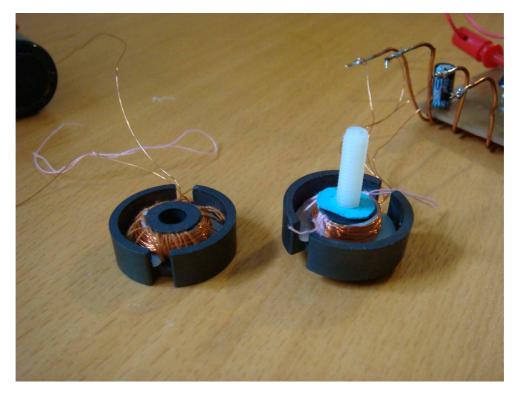

| Figure 17: Pot-Core                                                                                                               |    |

| Figure 18: Dimensions and behavior of AMIDON's pot-cores                                                                          |    |

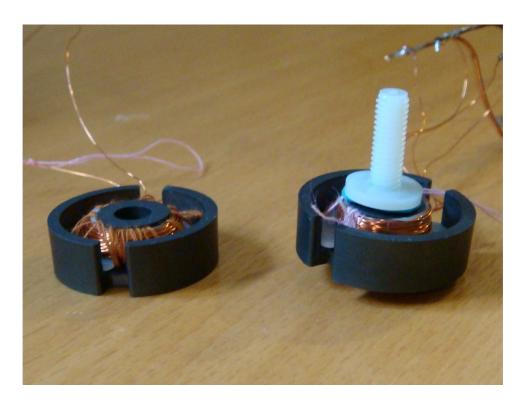

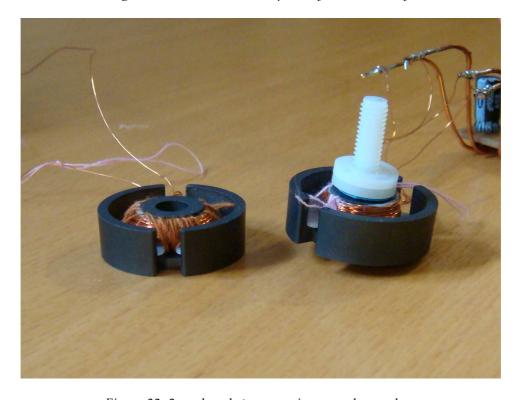

| Figure 19: Fixed primary side                                                                                                     |    |

| Figure 20: Portable secondary                                                                                                     |    |

| Figure 21: Views of the pad (upper lefthand corner), and Rail (upper righthand corner), and combinations of them                  |    |

| (the lower row)                                                                                                                   |    |

| Figure 22: Schematic of the test system for test #2                                                                               |    |

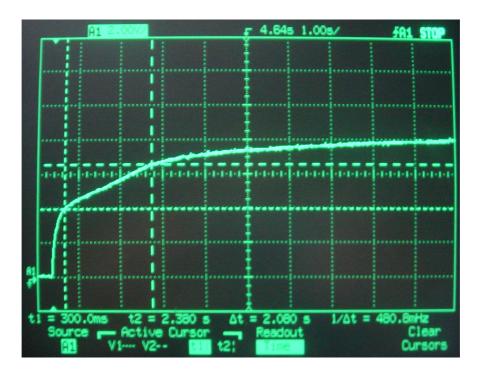

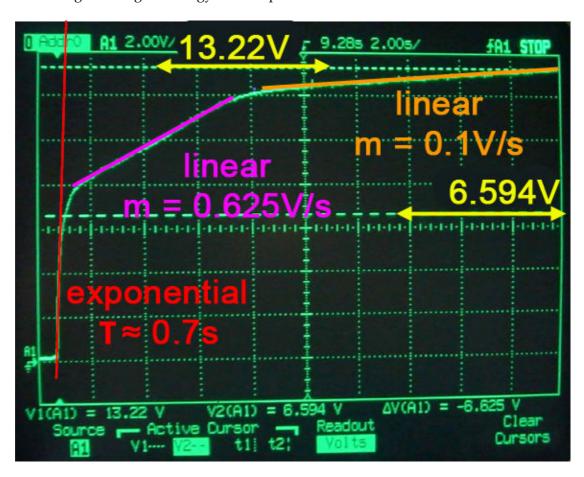

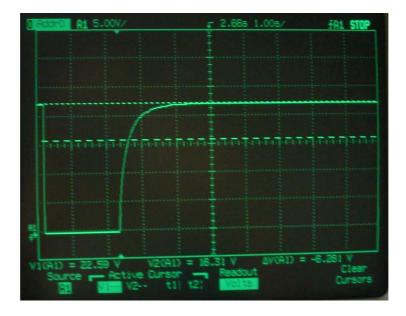

| Figure 23: $V_c(t)$ when charging the capacitor connected to the secondary arm                                                    |    |

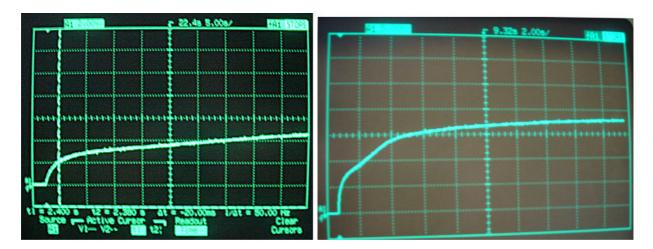

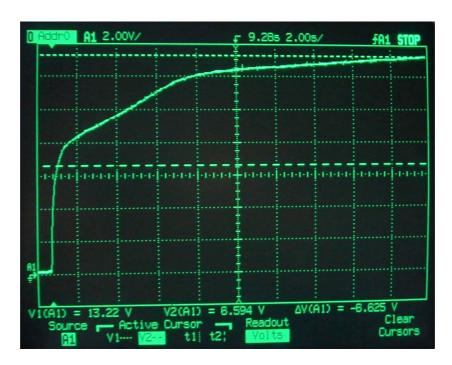

| Figure 24: $V_c(t)$ with test#3.1 configuration (left, 5s/div), $V_c(t)$ with test#3.2 configuration (right, 2s/div)              |    |

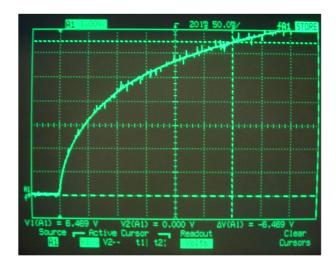

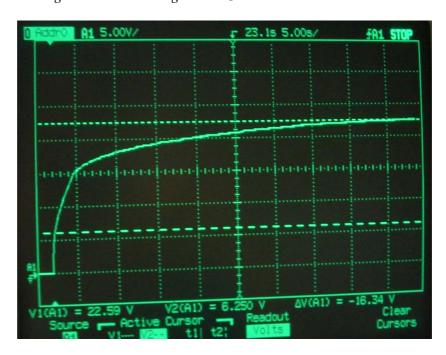

| Figure 25: V <sub>C</sub> (t) with test#4 configuration                                                                           |    |

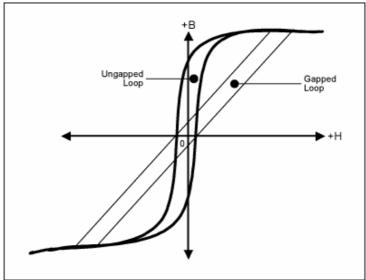

| Figure 26: Magnetization loops for a ferrite transformer with and without an air gap. Notice the increased transfe                |    |

| energy ΔH when a large air gap is used [40]                                                                                       |    |

| Figure 27: Coil assortment                                                                                                        |    |

| Figure 28: Test#5 configuration                                                                                                   |    |

| Figure 29: Close view of the stack closed                                                                                         |    |

| Figure 30: Card between primary and secondary                                                                                     |    |

| Figure 31: 1 washer between primary and secondary                                                                                 |    |

| Figure 32: 2 washers between primary and secondary                                                                                |    |

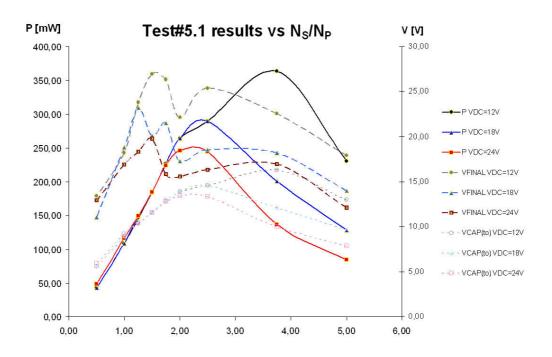

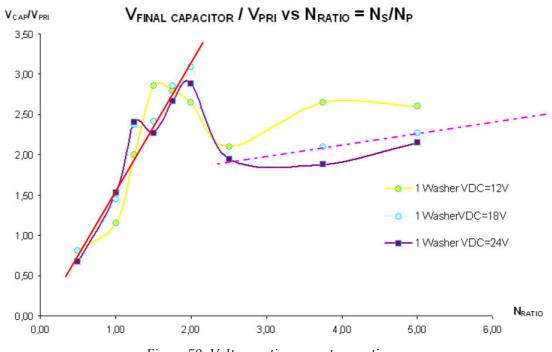

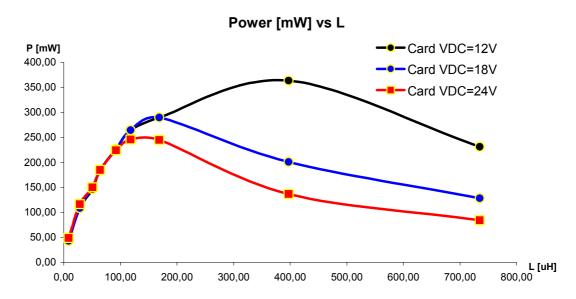

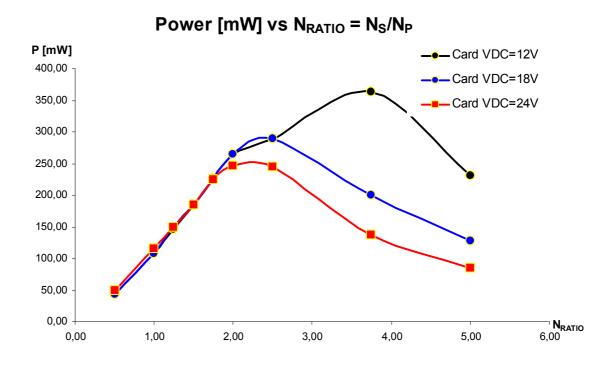

| Figure 33: Test#5.1 summary                                                                                                       |    |

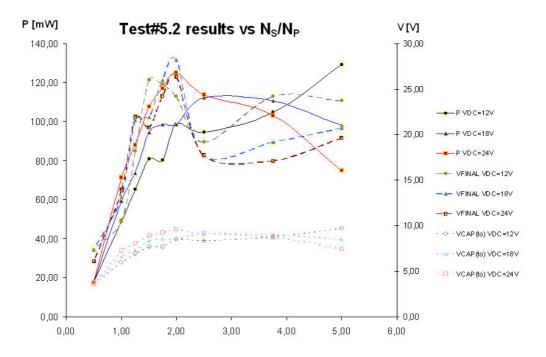

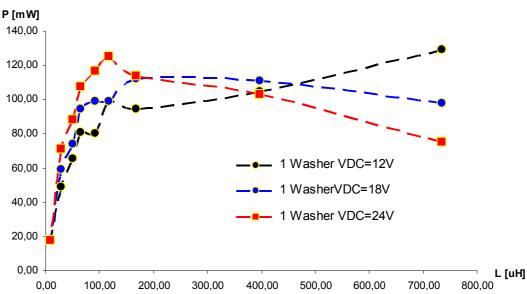

| Figure 34: Test #5.2 summary                                                                                                      |    |

| Figure 35: Test#5.3 summary                                                                                                       |    |

| Figure 36: System regulation                                                                                                      |    |

| Figure 37: General sketch of the Current Controlled Mode Pulse Width Modulator                                                    |    |

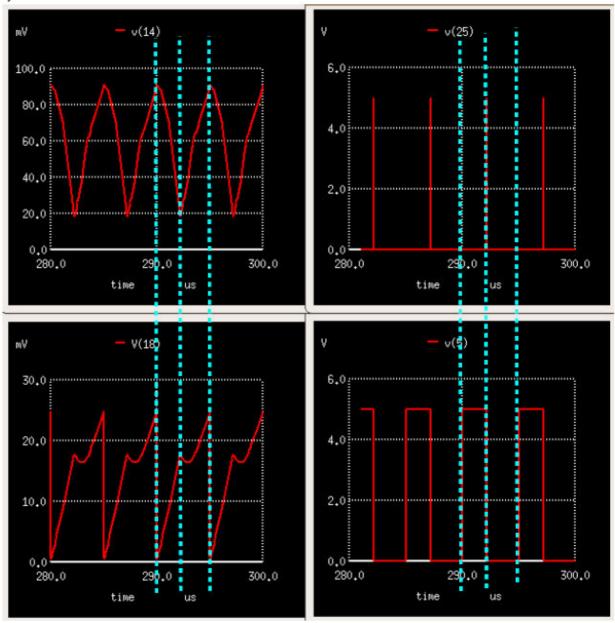

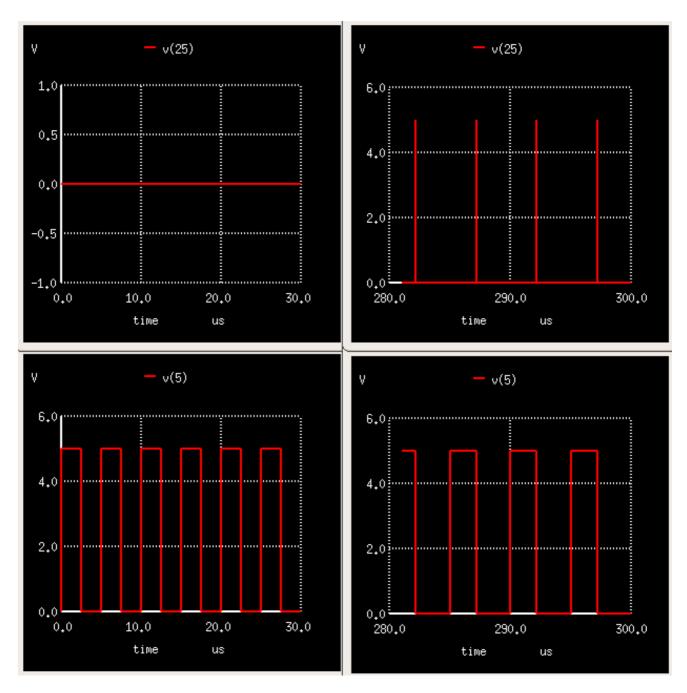

| Figure 38:(right, upper and lower): V(25) is OUT_COMP, when it goes up indicating regulated output, that the                      |    |

| current is too high, or that the DUTY CYCLE LIMIT has been reached, then, the transistor is switched OFF as                       |    |

| indicated in the plot of V(5) corresponding to the MOSFET gate voltage (where HIGH voltage means ON)                              | 47 |

| Figure 39(left, upper and lower): $V(14)$ is the voltage sensed through the coil while $V(18)$ is the voltage presented           |    |

| the controller at $I_{\text{SENSE}}$ pin, the addition of the (scaled signal V(14)) and the compensation ramp. Using the vertical |    |

| blue lines one can see that the peak of V(18) is when the MOSFET is turned ON and the signal V(25) turns the                      |    |

| MOSFET OFF                                                                                                                        | 47 |

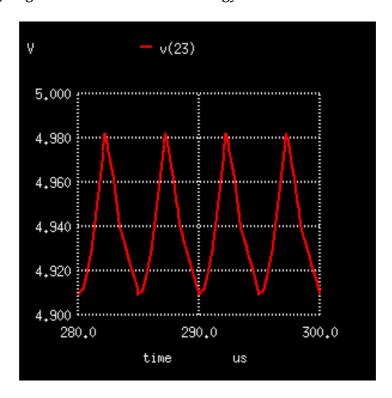

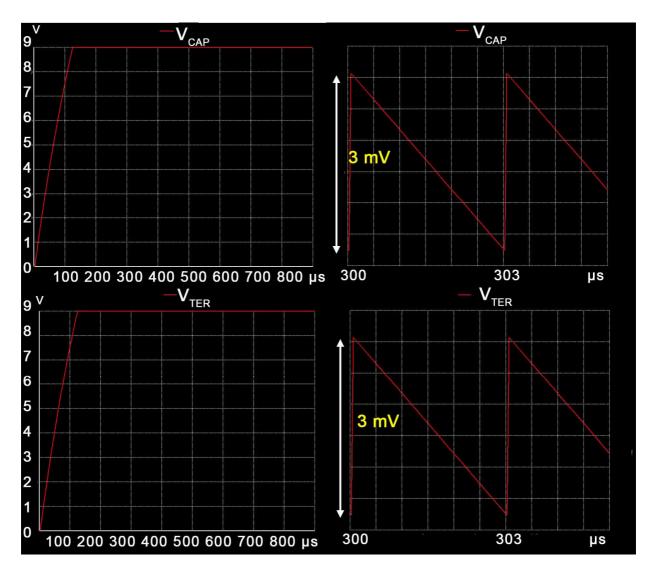

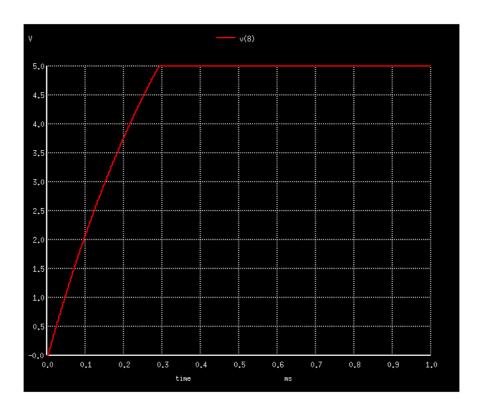

| Figure 40: Ripple observed at V <sub>OUTPUT</sub> when it is regulated to 5V                                                      |    |

| Figure 41(left, upper and lower): OUT_COMP and SET signal at the beginning                                                        |    |

| Figure 42 (right, upper and lower): OUT_COMP and SET signal with V <sub>OUT</sub> regulated                                       |    |

|                                                                                                                                   |    |

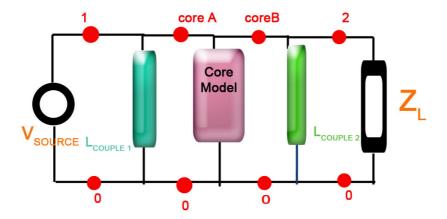

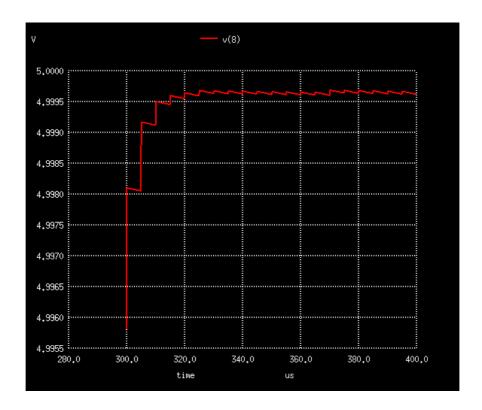

| Figure 43: 2-arms transformer with non linear core                                                                                      |      |

|-----------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 44: built.cir schematic                                                                                                          |      |

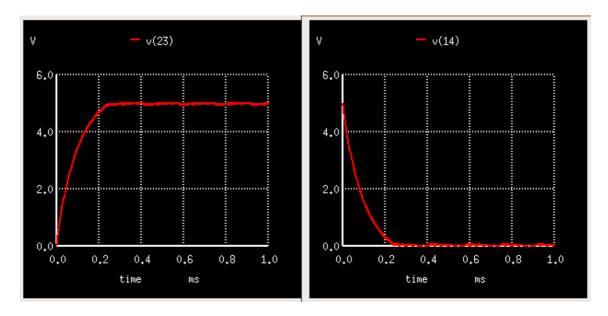

| Figure 45: Convergence on the output voltage at the secondary (mobile part)                                                             |      |

| Figure 46: Convergence on the voltage at the tertiary arm (embedded FB path)                                                            | 52   |

| Figure 47: Controlled ripple at the secondary arm, output at the mobile part.                                                           |      |

| Figure 48: Controlled ripple at the tertiary arm                                                                                        | 52   |

| Figure 49: Horizontal alignment                                                                                                         |      |

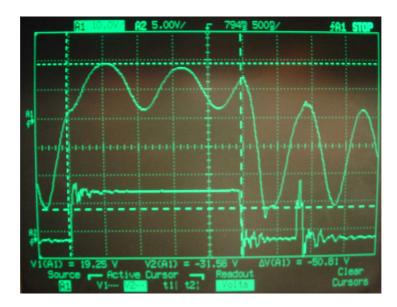

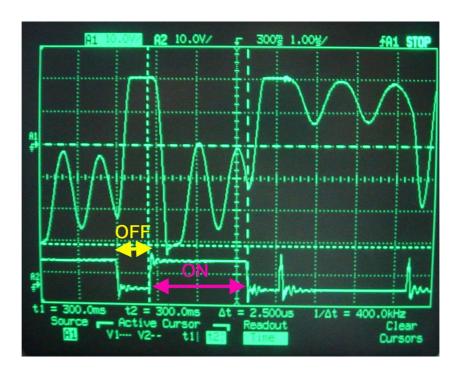

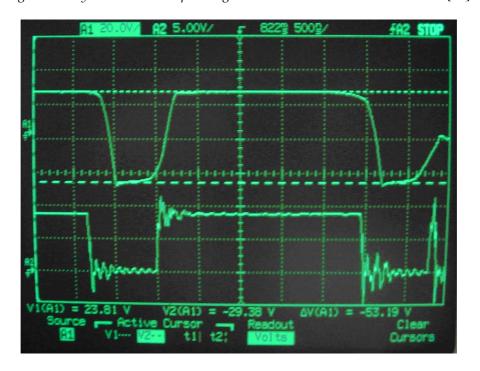

| Figure 50: V <sub>SEC COIL</sub> (upper) vs NDRV (lower) with faint magnetic coupling                                                   |      |

| Figure 51: Side core view when secondary placed on top                                                                                  |      |

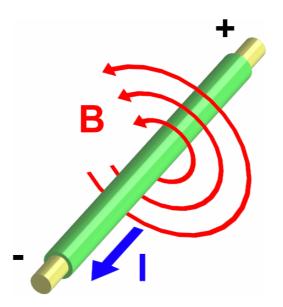

| Figure 52: Magnetic field rotating around the wire, direction defined by the current [57]                                               | 57   |

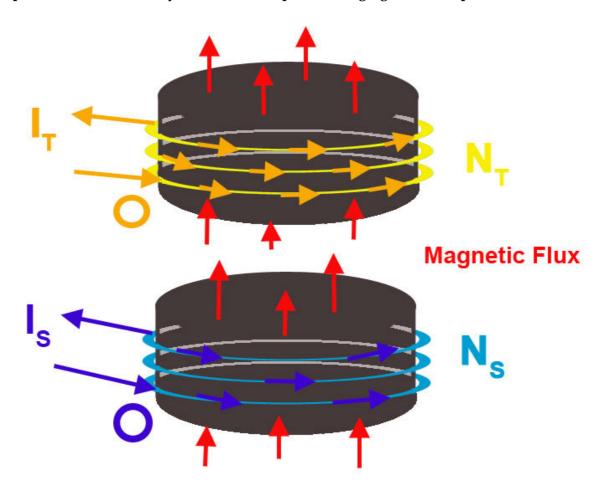

| Figure 53: Electrical equivalence between transformer arms                                                                              | 58   |

| Figure 54: V <sub>SEC</sub> (upper), NDRV (lower) when secondary soldered wrongly, with phase opposition                                | 59   |

| Figure 55: Different stages during the charging process                                                                                 |      |

| Figure 56: N <sub>S</sub> =75, V <sub>DC</sub> =12V, Card configuration where slope changes are hard to see due to the fast convergence | e 61 |

| Figure 57: Trend change with $N_S$ = 20 observed around 8V                                                                              | 62   |

| Figure 58: Trend change with $N_S$ = 50 observed around 17V                                                                             | 62   |

| Figure 59: Voltage ratio versus turn ratio                                                                                              | 63   |

| Figure 60: Lower power observed with smallest N <sub>S</sub>                                                                            | 64   |

| Figure 61: Optimization through higher V <sub>COIL</sub>                                                                                |      |

| Figure 62: Array of primaries                                                                                                           |      |

| Figure 63: Switching Power Conversion                                                                                                   |      |

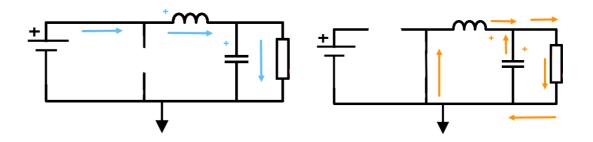

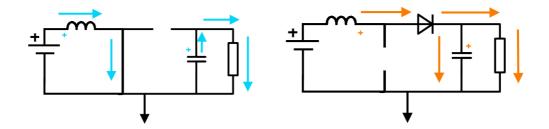

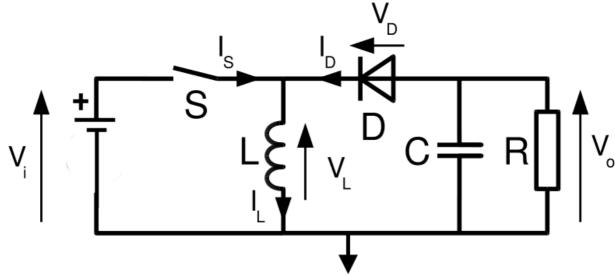

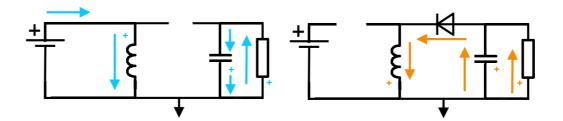

| Figure 64: Positive-to-Postive Buck Topology                                                                                            |      |

| Figure 65: Current when switch: ON                                                                                                      |      |

| Figure 66: Current when switch: OFF                                                                                                     |      |

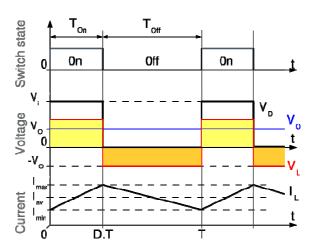

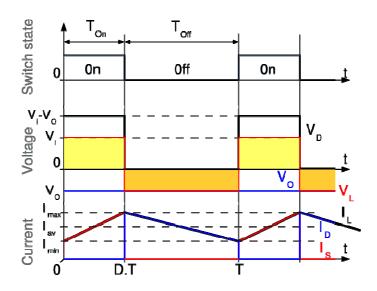

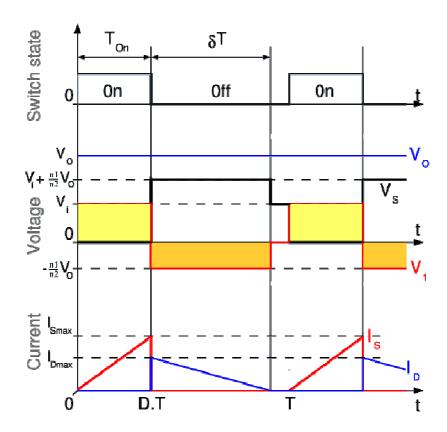

| Figure 67: Time diagrams, provided Continuous Conducting Mode                                                                           |      |

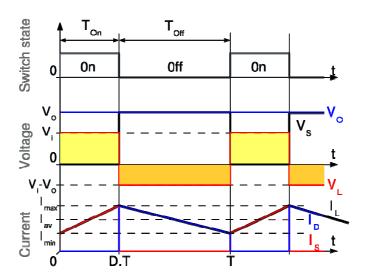

| Figure 68: Positive-to-Postive Boost Topology                                                                                           |      |

| Figure 69: Current when switch: ON                                                                                                      |      |

| Figure 70: Current when switch: OFF                                                                                                     | 75   |

| Figure 71: Time diagrams, provided Continuous Conducting Mode                                                                           |      |

| Figure 72: Positive-to-Negative Buck-Boost Topology                                                                                     |      |

| Figure 73: Current when switch: ON                                                                                                      |      |

| Figure 74: Current when switch: OFF                                                                                                     |      |

| Figure 75: Time diagrams, provided Continuous Conducting Mode                                                                           |      |

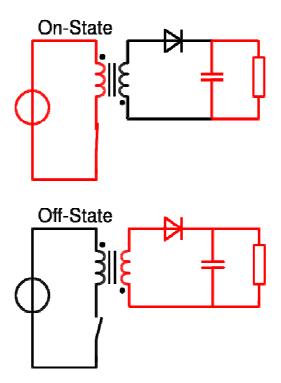

| Figure 76: In red, current flow in a flyback converter [42] (switch ON upper, switch OFF lower)                                         |      |

| Figure 77: Flyback converter operating on Discontinuous Conduction Mode [42]                                                            |      |

| Figure 78: Voltage at the secondary coil (upper) vs V <sub>CONTROL SWITCH</sub> (lower)                                                 |      |

| Figure 79: Equivalent circuit of the Buck regulator which was simulated                                                                 |      |

| Figure 80: $V_{OUT}$ convergence to $2xV_{REF}$ (left); $V_{ERROR}$ returns to zero when $V_{OUT}$ is regulated (right)                 |      |

| Figure 81 : Equivalent circuit of the simulated flyback converter                                                                       |      |

| Figure 82: Convergence at the output of the Flyback Converter                                                                           |      |

| Figure 83: Regulated output of the flyback converter, constant average with controlled ripple                                           |      |

| Figure 84: Flyback converter with three arms                                                                                            |      |

| Figure 85: Built circuit's simulation schematic                                                                                         |      |

| Figure 86: Comparative among data collected in test#51 with different $V_{DC}$                                                          |      |

| Figure 87: Comparative among data collected in test#51 with different $V_{DC}$                                                          |      |

| Figure 88: Comparative among data collected in test#52 with different $V_{DC}$                                                          |      |

| Figure 89: Comparative among data collected in test#52 with different $V_{DC}$                                                          |      |

| Figure 90: Comparative among data collected in test#52 with different $V_{DC}$                                                          |      |

| Figure 91: Comparative among data collected in test#53 with different $V_{DC}$                                                          |      |

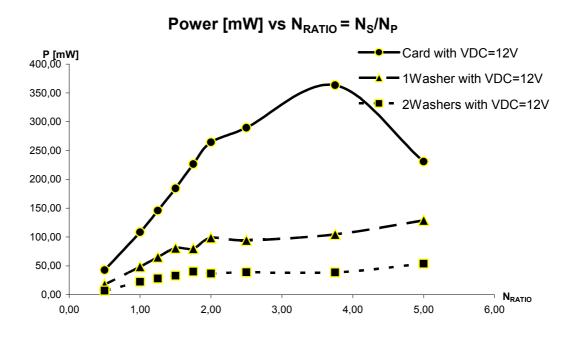

| Figure 92: Comparative among data collected in different tests with the same $V_{DC} = 12V$                                             |      |

| Figure 93: Comparative among data collected in different tests with the same $V_{DC} = 12V$                                             |      |

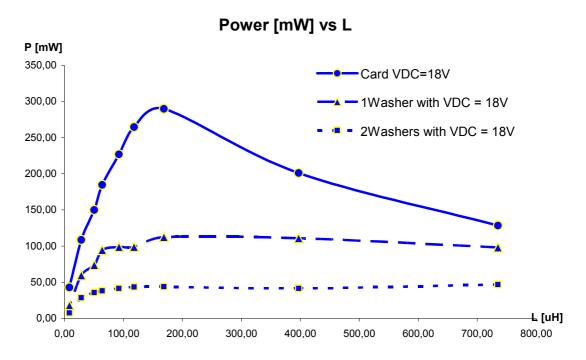

| Figure 94: Comparative among data collected in different tests with the same $V_{DC} = 18V$                                             |      |

| Figure 95: Comparative among data collected in different tests with the same $V_{DC} = 18V$                                             |      |

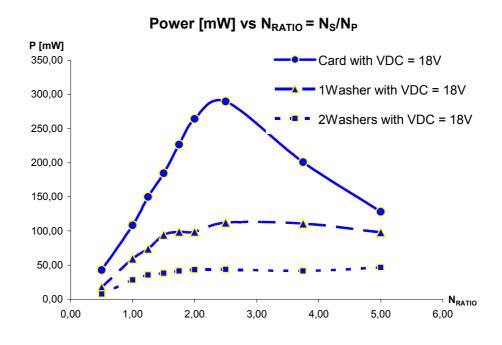

| 1 13 WIC DO, COMPANIATION WITH CONTROL IN AUTOCICAL THE WITH LIGHT WITH THE DUTTE VINC 10 V                                             | 10/  |

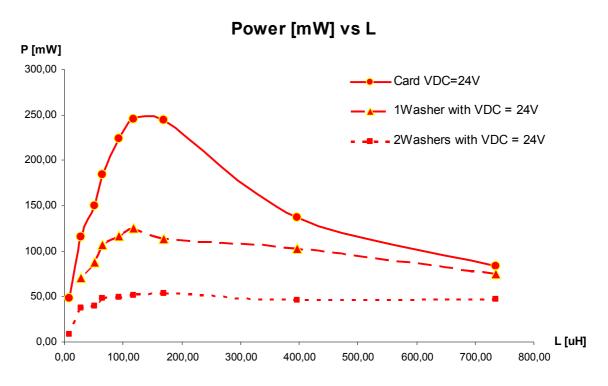

| Figure 96: Comparative among data collected in different tests with the same $V_{DC} = 24V$ | 108 |

|---------------------------------------------------------------------------------------------|-----|

| Figure 97: Comparative among data collected in different tests with the same $V_{DC} = 24V$ | 108 |

# Table of Tables

| Table 1: Initial components calculation                                                                              | . 17 |

|----------------------------------------------------------------------------------------------------------------------|------|

| Table 2: Initial components calculation (cont.)                                                                      | . 17 |

| Table 3: Modifications ensuring FB to receive a correct value                                                        | . 21 |

| Table 4: Measures comparing different materials (values from [34]) and measured core behavior                        | . 23 |

| Table 5: Refined component values                                                                                    | . 25 |

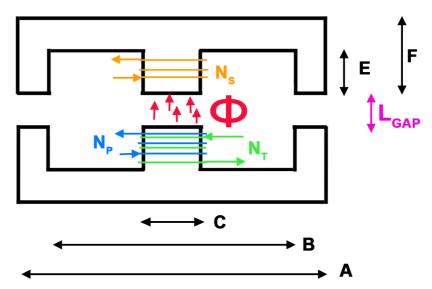

| Table 6: Dimensions of the chosen cores                                                                              | . 27 |

| Table 7: Magnetic Dimensions using the chosen cores at $f_{SW} = 20$ KHz). Subscript e indicating magnetic effective | . 27 |

| Table 8: Different values for different sizes of Pot-Cores                                                           | . 27 |

| Table 9: Values on the initial configuration                                                                         | . 28 |

| Table 10: Test#3 results                                                                                             |      |

| Table 11: Test#4 initial configuration                                                                               | . 35 |

| Table 12: Test#4 results compared with test#3 results                                                                | . 36 |

| Table 13: Test#5 separators thickness                                                                                | . 39 |

| Table 14: Test#5 initial configuration                                                                               | . 39 |

| Table 15: Modifications to provide a realistic simulation                                                            | . 50 |

| Table 16: Achieved operating time of different low power devices                                                     | . 65 |

| Table 17: Data collected in test#5.1 with $V_{DC}$ = 12 $V$                                                          | . 98 |

| Table 18: Data collected in test#5.1 with $V_{DC}$ = 18V                                                             | . 98 |

| Table 19: Data collected in test#5.1 with $V_{DC}$ = 24V                                                             | . 99 |

| Table 20: Data collected in test#5.2 with $V_{DC}$ = 12V                                                             | . 99 |

| Table 21: Data collected in test#5.2 with $V_{DC}$ = 18V                                                             | 100  |

| Table 22: Data collected in test#5.2 with $V_{DC}$ = 24V                                                             | 100  |

| Table 23: Data collected in test#5.3 with $V_{DC}$ = 12V                                                             |      |

| Table 24: Data collected in test#5.3 with $V_{DC}$ = 18V                                                             |      |

| Table 25: Data collected in test#5.3 with $V_{DC}$ = 24 $V$                                                          | 102  |

# List of Abbreviations and Acronyms

B Magnetic flux density or magnetic field, measured in units of tesla (T)

CCMPWM Current Controlled Mode Pulse Width Modulator

FB Feedback

f<sub>SW</sub> Switching frequency

H Magnetic field strength, measured in units of Amperes per meter (A/m) N<sub>P</sub> Number of turns of wire wound around the primary core forming the primary

transformer arm, generating the magnetic field

Ns Number of turns of wire wound around the secondary core forming the

secondary transformer arm, taking energy from the generated field and charging

the capacitor

N<sub>T</sub> Number of turns of wire wound around the primary core forming the tertiary

transformer arm, providing feedback about the field

P Primary arm of the flyback transformer

RFID Radio Frequency Identification technology

S Secondary arm of the flyback transformer

SMPS Switch Mode Power Supply

T Tertiary arm of the flyback transformer

M Magnetic permeability

Φ Magnetic flux, measured in units of weber (Wb)

## 1. Introduction

Although the new functionalities of mobile information technology (IT) devices seem to be limitless, batteries are still their weak point, thus this project studies a new way to wirelessly power mobile devices. As an evolution of the RFID tags' wireless powering procedure [11] where a passive tag can transmit data back by backscattering the field provided by the reader, new questions arise:

- If a near field effect will be used for some data exchange function, how much energy can be transferred to the mobile device at the same time?

- Can enough energy be transferred to power the device for a significant amount of time?

This design moves away from existing wireless chargers adapted to battery charging requirements, and innovates, by focusing on fast energy transfer based upon an intense, focused, and rapidly attenuated magnetic field produced with high magnetic permeability,  $\mu$ , materials and operated in the near field, d<0.16 $\lambda$ . The assumption is that energy will be buffered in a (super)capacitor ready to use. The problem this study addresses is how much useful energy can be transferred in a short amount of time.

## 2. Background/Related Research

Wireless is a key word today for most innovative IT products, with industry efforts oriented to providing integrated services with the highest commodities and facilities for users, without bothering the users about wires. Despite wireless communications being well established, annoying fixed wires or batteries (and battery chargers) are still required to power the devices. Consequently, major players in this field consider conveniently powering the device to be an unsolved issue, but potentially a likely profitable market, hence they have explored various solutions for wireless battery charging. Companies such as WildCharge [2] [3] have developed pads upon which devices are placed and recharged through an array of metal contacts, while SplashPower [4] [5] went further, by developping contactless systems which recharge the devices through inductive coupling. Fulton improved inductive coupling based charging system with intelligent adaptative control via their eCoupled™ system [6] [7], which utilizes feedback from individual devices in real time, modifying the charging parameters as needed. There remains a need to study the efficiency of these existing systems and to improve upon them. For example, SplashPower is using the Synopsys Saber Simulator to do this [8].

As services become more performance demanding, batteries become more of a limitation: On one hand, the efficiency of the widely used Li-Ion batteries decreases as the load decreases, something that happens as a result of the miniaturization of electronics [9]. On the other hand, these batteries have very strict guidelines that establish how they must be charged [10]. Thus, instead of providing energy to something which takes so a long time to charge and has very circumscribed requirements on voltage/current levels, an alternative is to buffering

energy for future use. The basic idea is derived from a study of RFID, Radio Frequency Identification, implementations but utilizing much higher strength fields in order to provide more than just the few milliseconds of operating time which an RFID chip requires.

RFID tags are generally passive devices powered by rectification of the magnetic (H) field which transmits information back to the reader by exploiting the power of the received field [11]. Note that even in case of active tags, the batteries are only used to power the chip, while the transmission power of the transponder comes from the received field. Unlike the previously mentioned battery charging systems, RFID generally works with only low power levels [12]. While the energy is adequate for tags it is insufficient to power more general IT devices, thus the concept has to be adapted to this different purpose. The search for high power transmission through a near inductive field implemented by an existing architecture led to the examination of Switching Mode Power Supplies [13]. Some basic concepts of these power supplies will be explained next, in order to justify this choice as our starting framework.

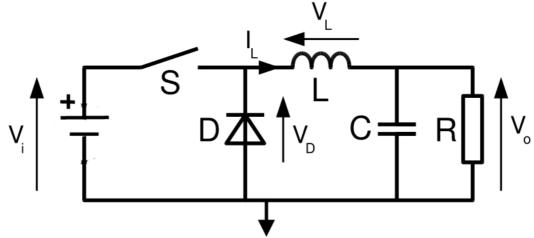

In Switching Power Conversion, energy is **continuously drawn** from an "input source", **chopped** into packets by means of a switch (transistor), then **averaged with** the help of an **LC** circuit in order to result in a continuous (constant average) transfer of energy. The result is that a **smooth** and steady flow of energy appears at the output.

*Figure 1: Switching Power Conversion*

Switching Mode Power Supplies (SMPS) convert input power, provided by a DC source, into a regulated DC voltage at the output. DC-DC SMPS are distinguished by being highly efficient when dealing with high power conversion. This is because energy is **only consumed when switching** between the ON and OFF states. Energy is not consumed by the power supply itself during the ON or OFF state because the transistor has *ideally* null current flowing through it when it is OFF and because the voltage drop between its terminals is *ideally* null when it is ON. Nevertheless, real implementations always have losses due to *leakage currents*, because there's still current flowing even in the OFF state, and *conduction loss* since the voltage difference between the terminals is not null when ON. Because of their long lifetime and high switching speed, N-channel MOSFET transistors are commonly used to build these power supplies. Such a transistor is a are voltage controlled device which generates unwanted noise and ripple that require high current levels (~1A) to achieve quick

switching. As a result, a high source voltage is needed to make the device work. In addition, these devices are a source of Electro Magnetic Interference (EMI).

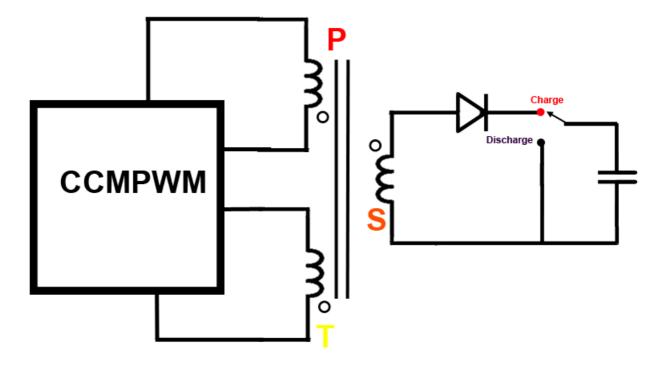

After reviewing all available topologies, the "Flyback Converter" (or "Flyback Transformer") [14] was chosen. Here the coil that is present in all SMPS architectures is substituted by a transformer. This seems the most suitable solution for this application because it provides electrical isolation between the primary and the secondary sides of the circuit and makes it possible to *split* the circuit and *separate* both parts so the primary side, containing the controller and all the circuitry related with the power supply can be located at the fixed part of the circuit, while the secondary (consisting of a coil, a rectifying diode, and the capacitor functioning as a buffer) will fit inside the tiny handheld device which wishes to receive the energy.

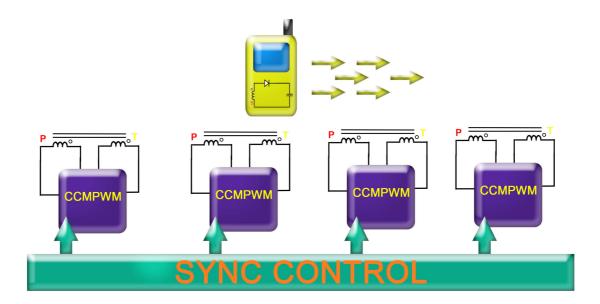

As a result, the innovation introduced by this research is the rapid energy transfer from a fixed device to a device which will be moving through the near inductive field existing between the primary and the secondary sides of a transformer. The final goal of this study is to predict how much energy could be coupled during a common situation, such as moving the device along an array of *primary sides* placed, for instance, in the turnstile at the entrance to the subway. As starting point, this thesis will focus on how much can be coupled from a single primary, to have an initial hint of the feasibility and performance of the system.

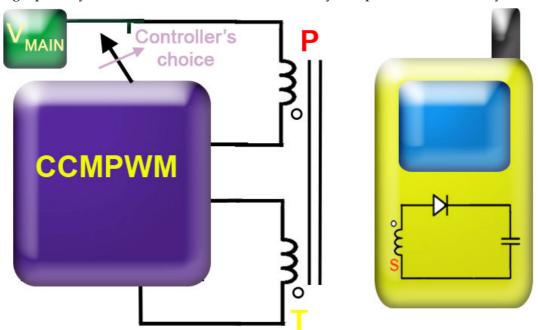

Figure 2: Simple sketch of the system

As shown in Figure 2, the basic structure of the system can be divided in two main parts. The primary arm, P, of the transformer generates a magnetic field with the energy from an external power supply. The controller regulates the output by switching between ON and OFF according to what is sensed through the Tertiary arm, T. This switching decision is made by a Current-Mode Pulse Width Modulator Controller (CCMPWM). Because a varying current through a coil results in a voltage according to equation (1) and this change in voltage

is mirrored at each of the coils (each with its specific inductance L) composing the transformer.

$$V_L(t) = L \frac{dI_L(t)}{dt}$$

(1)

Because the secondary side of the transformer, S, is placed inside the handheld device, it will only take energy from the field produced by the primary when it is close to the primary coil.

# 3. Method/approach

Before modelling, a real device was selected from the available choices of current controlled pulse width modulated controllers in the market in order to have a clear idea of what was necessary to simulate. The MAX5068E [15] from Maxim Integrated Products, Inc. was chosen for the system implementation because:

- It is a low cost readily available, current mode pulse width modulator controller.

- It is well suited for universal input (i.e., from any standard power mains supply), so it can handle high voltages, essential for this application.

- It allows switching frequencies ranging over **12.5..625 KHz**, which are high enough for the correct functioning of the magnetic field coupling through the transformer.

- It provides a SYNC input for synchronization to an external clock (making it easy to turn **the device ON** when another device with a secondary coil is over this specific primary coil in an array, such as might be placed at a turnstile).

- It has a **programmable** internal slope-compensation circuit which is used to stabilize the current loop; it operates at duty cycles over 50% (its maximum Duty Cycle is 75%): Instead of using this for regulation, it will be used to "fool" the circuit so as the maximum power is transferred to a supercapacitor placed at the secondary side of the transformer (this will be broadly explained in section 3.1.2.)

- It is a low cost chip (<US\$2) and it uses a tiny surface mount device package so that arrays of these devices and coils can easily and cost effectively be built

## 3.1. The configuration: Basic Parts, Functioning.

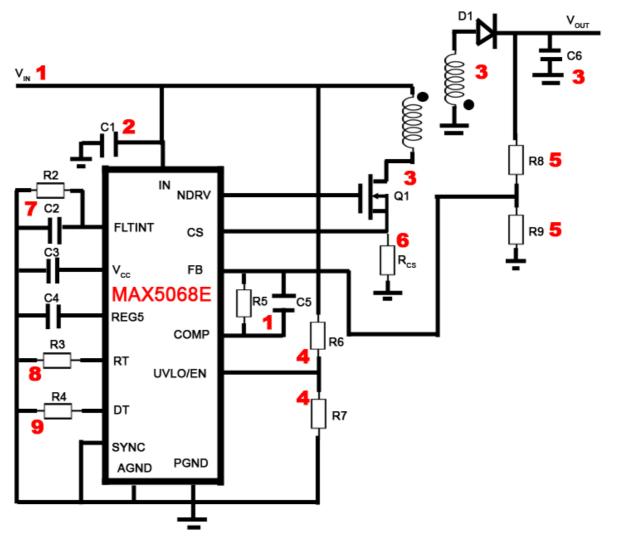

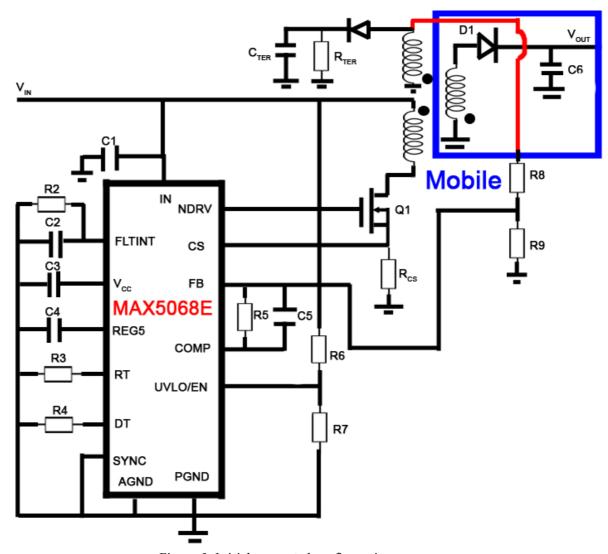

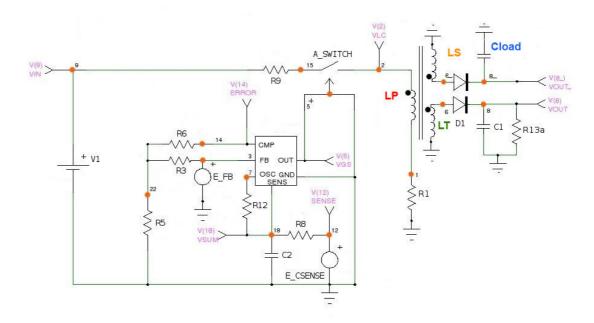

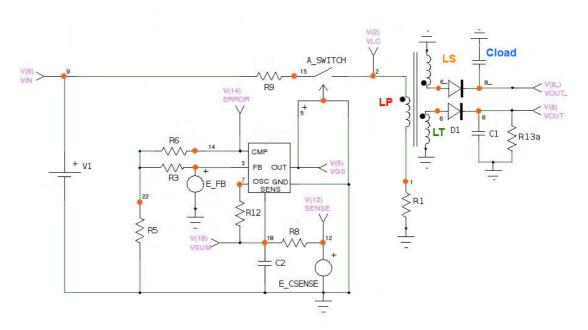

As marked on Figure 3, there are a number of pins with various functionalities to control an SMPS built with this CCMPWM. A detailed description of the pin functionality follows.

### 3.1.1. $V_{IN}$

As high as possible to maximize the power injection into the circuit ( $P \sim V \times I$ ) while maintaining reasonable component voltage ratings.

## 3.1.2. Reservoir capacitor

C1 should be at least 100  $\mu$ F (the value specified in the datasheet as typical) because it must be big enough to store enery during the 2047  $T_{CLK}$  cycles that the circuit's soft-start lasts.

## 3.1.3. Buck Regulator

The chip controls NDRV to switch Q1 between ON/OFF, while the energy is stored at the reactive elements (in this case the transformer coils) during the ON states and smoothly supplied during the OFF states, guaranteeing a regulated output. As seen from the theory regarding SMPS:

$$L \times I_{L} = \frac{V_{ON} \times D}{r \times f} = \frac{V_{ON} \times D}{f} \times \frac{1}{r} = \frac{E \times t}{r}$$

(2)

Figure 3: MAX5068E on the initial configuration

Since it is a *Buck regulator* where:

$$I_{o} = I_{L} \quad (3)$$

$$L = \frac{V_{ON} \times D}{r \times f \times I_{O}} \quad (4)$$

And where  $V_{ON} = V_{IN} - V_{OUT}$ , D = Duty Cycle established at 75% maximum, r = 0.4 (rule of thumb for the design),  $f = f_{SW}$ . For more information see appendix A.

The inductance of the transformer windings are a function of the number of turns, the dimensions of the coil, and the material of the core as shown in equation 5.

$$L = \frac{\mu_0 \mu_R N^2 A}{l} \tag{5}$$

$\mu_0$  is the permeability of free space ( $4\pi \times 10^{-7}$  H/m)  $\mu r$  is the relative permeability of the core (dimensionless) N is the number of turns. A is the cross sectional area of the coil in m<sup>2</sup> l is the length of the coil in m i is the current in A

Equation 6 gives the flux density.

$$B = \frac{Li}{NA}$$

(6)

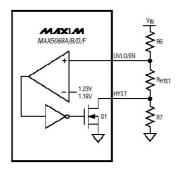

## 3.1.4. Reference Voltage Regulation Loop

**R**<sub>HYST</sub>=0 (not shown in Figure 3 because the HYST pin is not available on the MAX5068E, the model of the device that is used) this means that the voltage indicating the change of cycle is the same to switch from ON→OFF as to switch from OFF→ON) **R6** and **R7** constitute a voltage divisor that will present at UVLO/EN the voltage indicating when NDRV should switch, hence causing the transistor to change between ON or OFF. Thus, in a SMPS R6 and R7 are calculated to achieve a desired V<sub>OUT</sub>.

Figure 4: UVLO/EN regulation circuit (appears here with the permission of the copyright owner)[15]

- When UVLO/EN rises over 1.23V, Q1 is turned ON by means of NDRV.

- When UVLO/EN falls under 1.18V, Q1 is turned OFF by means of NDRV.

As a result regulation is achieved by switching between two states where the reactive elements charge/discharge alternate creating a smooth energy flow at the output provinding feedback information.

$$R6 = \left(\frac{V_{ON}}{V_{ULR2}} - 1\right) \times R7 \tag{7}$$

In equation 7,  $V_{ON} = V_{IN} - V_{OUT}$ ;  $V_{ULR2} = UVLO/EN$  rising threshold = 1.231V

## 3.1.5. Internal Error Amplifier

**R8** and **R9** constitute a voltage divisor of  $V_{OUT}$  providing an **input to pin FB with a voltage proportional to V\_{OUT}. This voltage divisor is the key regulating the output, where the voltage level is chosen to provide FeedBack, FB. On top of that, by controlling the relation between these two resistors, it is establishes the voltage which the output will be regulated to.**

$$V_{OUT} = \left[ \left( 1 + \frac{R8}{R9} \right) \times V_{REF} \right]$$

(8)

In equation 8,  $V_{REF} = 1.23V$

The slope compensation internal circuit generates a ramp whose slope is determined by SR (see equation (9)) at f<sub>SW</sub> which is added to the current sensed through CS and compared with the output of the error amplifier, COMP, to decide whether NDRV should continue conducting after the initial spike or not.

The reason for adding this sawtooth whose frequency is the same as f<sub>SW</sub> to the current sensed is to increase stability and avoid oscillations:

"Ridley demonstrated that the Q becomes infinite at D=0.5 with no external ramp, which confirms the inherent instability of a current mode SMPS which has a duty cycle greater than 0.5." [25]

$$SR = 90mV/\mu s = \frac{165 \times 10^{-6}}{R_{RT} \times C_{SCOMP}} = \frac{N_S \times K \times R_{CS} \times V_{OUT}}{N_P \times L}$$

(9)

In equation 9,  $N_P$  and  $N_S$  are the number of turns at the primary and secondary side of the transformer (in our application,  $N_S << N_P$ ), K=0.75, L is the secondary filter inductor (whose value depends also on  $N_S$ );  $V_{COMP}$  is in the range of [0.4V, 1.1V] in the Low (OFF) case or  $V_{COMP}$  is in the range of [2.6V, 3.8V] in the High (ON) case, thus the output voltage of the internal error amplifier is minimized when  $V_{OUT}$  reaches the desired value.

### 3.1.6. Current Sensing through the Primary Arm of the Transformer

R<sub>CS</sub> presents a voltage input to current sense, CS, proportional to the current flowing through the primary arm of the transformer. After adding this to the slew rate, SR, the sawtooth waveform is compared at the pulse width modulator, PWM, comparator with the error amplifier output, to determine if NRDV should be switched off:

$$I_{PRIMARY} \times R_{CS} > (V_{EA} - V_{OFFSET} - V_{SCOMP})$$

(10)

Equation 11 is used to limit the maximum current at the primary:

$$R_{CS} = \frac{V_{CS}}{I_{PRI}} \tag{11}$$

In equation 11,  $V_{CS} = 314 \text{ mV}$ ;  $I_{PRI} = I_{PEAK @ PRIMARY CIRCUIT}$

### 3.1.7. IC protection against transient overcurrents

$$C_{FLINT} = \frac{I_{FLINT} \times t_{SH}}{2.8}$$

$$R_{FLINT} = \frac{t_{RT}}{0.595 \times C_{FLINT}}$$

(12)

(13)

In equations 12 and 13,  $t_{SH}$  = Shutdown time of the circuit,  $I_{FLINT}$  = 60  $\mu$ A,  $t_{RT}$  = 10  $\times$   $t_{SH}$

### Switching frequency (f<sub>SW</sub>) 3.1.8.

$$R_{RT} = \frac{10^{11}}{4 \times f_{cur}} \tag{14}$$

The switch will turn ON at the beginning of each cycle, creating at least, spikes at a rate indicated by f<sub>SW</sub>. Equation 14 described how resistor R<sub>RT</sub> determines this frequency.

The MOSFET can either keep on conducting current during, at maximum, the time indicated by (Duty Cycle)\*T<sub>CLK</sub> or not. It will not conduct if V<sub>OUT</sub> is high enough or there is too much current flowing through the coil (measured by CS) or other exceptions like Thermal Shutdown, Digital Soft-Start or Dead Time (will only turn it off after conducting during a whole duty cycle).

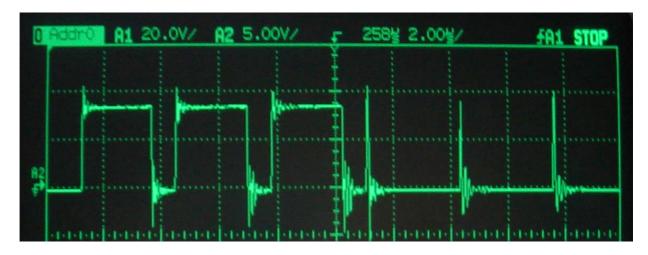

Figure 5: NDRV ON at 75% Duty Cycle (left); spikes when NDRV should be OFF (right)

## 3.1.9. Dead Time: Duty Cycle time decrease

$R_{DT}$  can be used to slightly decrease the time of the maximum allowed Duty Cycle (in any case, it will never be greater than 75% of  $T_{CLK}$  ON) to prevent transformer saturation at the primary side. This is established by the Dead Time as described on equation 15:

$$DT[ns] = \frac{60 \times R_{DT}[k\Omega]}{29.4} \tag{15}$$

# 3.2. Topology modifications: From suggested to desired implementation and function.

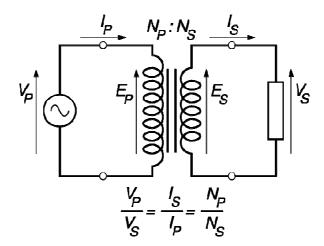

In this study a **separable** SMPS is required as a basic component. So, there cannot be any control loop directly connecting the energy buffer output with the controller, i.e., without using a wire or another connection i.e. LED + Optical Sensor. Otherwise the mobile device would need to be tethered in some way to the controller. This separable solution based on a transformer[16] is shown on Figure 6:

Figure 6: Ideal transformer behavior [16]

Current will start flowing when a load is placed at the secondary. This current will generate a magnetomotive force over the secondary winding that will oppose the primary. As a result, the flux on the core will be reduced [17]. Since this flux decrease will also reduce the back electromotive force, emf and disturb the equilibrium of the primary circuit [18] the current in the primary will rise, increasing the core flux until the supply voltage is again matched and the effect of the energy taken from the secondary will be compensated for [19]. Consequently, the core flux and both primary and secondary emfs remain the same, regardless of the secondary current, as they are determined only by the voltage at the primary side of the transformer. Therefore energy fed into the primary is transferred to the secondary. [16]

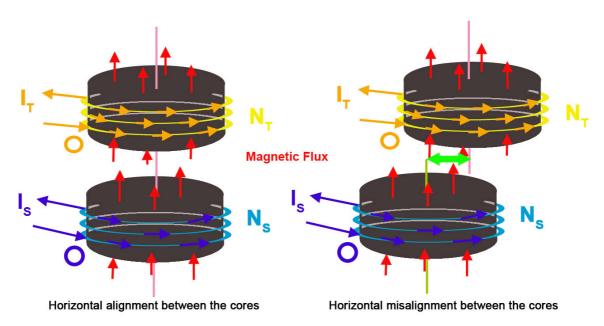

This behaviour of transformers is exploited as shown in Figure 8 to form a separable circuit while maintaining proper closed-loop operation of the controller by adding a tertiary winding to the transformer permanently co-located with the primary winding. The tertiary winding will cause the controller to attempt to maintain proper closed-loop operation regardless of the location of the secondary. The secondary is usually absent, and only sometimes placed close enough to collect magnetic field lines and therefore, energy; this balance (or imbalance) (between *supplier* and *consumers* of energy) would appear, at the same time in the secondary and tertiary:

- Secondary away: The controller switches NDRV between ON/OFF to mantain a constant average  $V_{\text{OUT}}$  as sensed through the FB path. The energy consumed by the load on  $V_{\text{out}}$  is simply wasted energy.

- Secondary on top of the primary (and tertiary): When the secondary coil approaches, magnetic flux coming out of the primary half-core will go into the secondary, generating a magnetic flux there, thus energy will be transferred in this way from the primary to the secondary coil. Additionally, more energy will be supplied by the primary until the V<sub>OUT</sub> (sensed as the output the load by the tertiary coil, placed in the fixed part of the circuit), sensed as FB (as before), results in a regulated voltage value. This means that during the imbalance the secondary rapidly receives power from the primary, until the tertiary is back in regulation, at which point the secondary reaches

a voltage which is is proportional to the voltage on the tertiary (in proportion to the number of windings, assuming that the cores are the same diameter and aligned). This occurs because when back in regulation the ratio of voltage in the primary and tertiary is proportional to the number of turns about the primary and tertiary, which are ideally always aligned.

In other words, the effect of the *load* (in this application, a capacitor buffering energy, placed inside the handheld device and attached to the secondary) will show up at the tertiary arm (that also has a load), in the fixed part of the circuit, as a result of magnetic coupling, without requiring any other kind of connection.

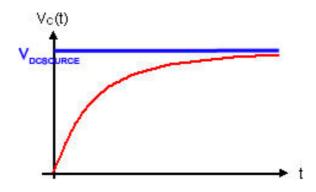

It's known that the effective impedance of a capacitor varies even while being charged to a constant DC voltage. It draws more current at the initial stage. There is no strict regulated source requirements in order to place energy into the buffer so the variations in the current while the capacitor is charging and while the SMPS is trying to bring the output back into regulation (based upon FB) will not damage the capacitor, as long as the voltage across the capacitor voltage is less than or equal to its voltage rating.

$$V_{C}(t) = V_{DCSOURCE} \times \left(1 - e^{\frac{-t}{RC}}\right)$$

$$i_{C}(t) = C \times \frac{dV_{C}(t)}{dt}$$

(16)

The behavior of a capacitor charging from an ideal independent voltage source ( $V_{DCSOURCE}$ ) is shown in Figure 7 and described by equations 16 and 17. In this solution  $V_{DCSOURCE}$  is dependent because of the closed-loop nature of the controller. Therefore the shape of the capacitor charging curve using the circuit described in Figure 8 will deviate from the ideal. This is described in detail later in the thesis.

Figure 7: Capacitor charge through a RC series circuit

Figure 8: Initial suggested configuration

## 4. Computer Model of a generic SMPS

# 4.1. Choice of Simulation Environment

As stated before, the purpose of this study is to transfer energy through magnetically coupled coils via an inductive field in the Near Field zone, which could occur while sliding one secondary coil past an array of other primary coils. The energy is to be transferred to a secondary coil where it will be buffered on a capacitor in order to supply power to a mobile device. As part of this project we want to design, optimize, measure, and evaluate a single cell of such an array of primary coils. One of the best ways of designing and optimizing any circuit is to build a detailed model where element values and/or topologies may be easily modified. Additionaly, there is no risk of hurting anyone by using high voltages, as might

occur when experiments are performed to determine where the physical limits are. The modelling language used is a modified version of SPICE [20] [21]. Although SPICE has a long history of use for integrated circuit design, it is unable to simulate hybrid (analog-digital) circuits simultaneously nor to simulate magnetic hysteresis (nonlinear magnetic core behavior) [24]. However, the later is present at the transformer with a ferrite core (which has been used to increase the magnetic field intensity) through which the coupling between primary and secondary sides is done. Literature research [25] was conducted to find a suitable simulation solution. This literature study uncovered Steven M.Sandler's, book "Switchmode Power Supply Simulation with Pspice and SPICE3" [25].

Pspice [26], allows advanced simulation of analog & mixed-signal environments. Initially this appeared to offer the best alternative, but after some difficulties finding a Linux version of PSpice, an open source software package for Linux, ngspice [27] was chosen. Ngspice contains Xspice [28] which supports the mixed-mode and non-linear simulation requirements. It is an extension to the SPICE3 simulator providing the ability to use code based models written in the C programming language to add new user-defined models when the element needed is not already implemented by the XSPICE model library. This library contains over 40 new functional blocks including summers, multipliers, integrators, magnetic models, limiters, S-domain transfer functions, digital gates, digital storage elements, and a generalized digital state-machine. How these models were used and extended is described in the next section.

## 4.2. Simulation Approach Method

Sometimes integrated circuit vendors provide SPICE models. While Maxim makes available many SPICE models, unfortunately they do not have one available for the MAX5068. This controller is the core of a Switching Mode Power Supply. Its purpose is the regulation of  $V_{\text{OUT}}$  by deciding when to switch the MOSFET between ON and OFF. The MAX5068 has high internal complexity, containing in addition to the basic regulation functions, a lot of extra circuitry intended to prevent damage to the IC and to control some internal functions not related to power supply operation. As it was not a concern of the thesis to consider all of these "corner" cases, the wisest option, rather than model the complete controller was to simply model its switch mode power supply behaviour, i.e. its regulation of the MOSFET during normal operation.

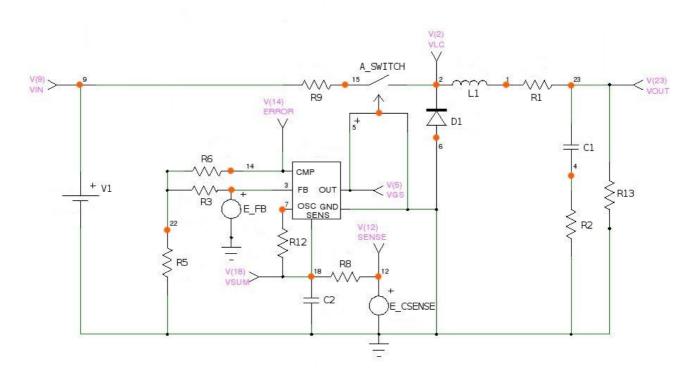

A literature study led to an article by Christophe Basso on writing models for power supply controllers [29]. Even if architectures for SMPSs are complicated, such as the one for the MAX5068 as shown in Figure 10, the core functionalities are the same. The secondary functions (such as the pins and functional units used to supply the chip with regulated power or the control loops to protect them against overcurrent situations) can be optionally modelled. By only modelling the core funtionalities, a very simple model of such a current control pulse width modulator controller (shown in Figure 9) can be used in a XSpice circuit description. This model leads to a very simple suggested circuit realization, shown in Figure 10.

Figure 9: The internal circuitry of a generic single output CCM PWM controller [29]

Figure 10: Suggested architecture for a current-mode controlled Buck regulator (see appendix A.2.1. for more information about Buck regulators) [29]

Figure 11: Internal MAX5068 configuration (with permission from the copyright owner)[33]

Comparing Figure 9 and Figure 10 with the internal block of the MAX5068 shown in Figure 11 a number of equivalences can be seen.

- The **PWM COMPARATOR** is the current limit comparator between the voltage generated by the current through CS (**I**<sub>CS</sub>**xR**<sub>CS</sub>) and the output of the Error Amplifier, called the Current Comparator in the simplified model. Therefore, **CS** of MAX5068 is the equivalent pin to ISENSE here.

- The **Error Amplifier** with feedback is the same in both.  $V_{REF}$  in the generic model is fixed at 1.23V in the MAX5068.

- The pin named NDRV used to switch the MOSFET of the SMPS between ON/OFF is more or less the same as the Output Driver of the generic model (more signals are taken into account in the MAX5068, because it is a more complex circuit which includes several more control loops). In the generic model, the Output Driver is turned OFF when the current coming from ISENSE is greater than the output of the error amplifier (coming from the comparison between Vref and FeedBack voltage) the functioning is exactly the same in MAX5068. However, in order to see it clearly it should be noted that even though

connections are done in the opposite way, there is a NOR logic gate which will turn the latch OFF whenever one of the inputs (no matter which) is '1'.

- **SYNC**, providing synchronization to an external clock is the equivalent to the ENABLE pin.

- **COMP** of the MAX5068 is the equivalent to OUT in the generic model, this is only a control pin to reveal what is happening at the output of the Error Amplifier.

Even if the suggested architecture for a SMPS using the MAX5068 datasheet may seem more complicated, the primary differences are the result of supplying the circuit with DC power that involves pins IN & REG5 as well as the functional unit REGULATOR. The generic model has no equivalent, as it simply assumes that there is suitable available power supply for the controller itself. Finally, UVLO/EN programs the input-supply STARTUP voltage and ensures proper operation during brownout conditions. This circuit also has no equivalent in the generic model, because the model has assumed that there is always sufficient power coming into the device. The OSC signal in the simplified model is simply a ramp compensating signal. The MAX5068 incorporates an adder to achieve slope compensation that is not included in the generic model of the CCMPWM, but implemented at node 18 in the circuit shown in Figure 10. This same approach is used in the circuit which was built and simulated, thus the ISENSE (pin 18 in Figure 10) comes from the addition of the slope and the current sensed. However, this is done outside of the controller in the simplified model.

Many elements of the MAX5068 were simply removed because they had no relevance at this stage in the modelling. For example, DT only provides a small adjustment of the Duty Cycle. FLTINT provides a protection to ignore overcurrents in case they happen during a short period of time and RT is simulated in SPICE using a clock. Hysteresis, HYST, is not available on the version E of MAX5068 which is used in this application, hence it was not modelled. UVLO/EN is used at the start-up of the circuit as well as a protection to allow self-functioning even in brownout cases, therefore was not included in the simulated circuit. Note also that, in the real circuit, if VIN drops below 9.74V, then a Digital Soft-Start ("reboot" of the circuit) is done through node {1} on Figure 8. Even though this regulation is necessary, these elements were omitted at this stage of modelling.

As shown on Figure 11, an internal clamp circuit is used to prevent the bootstrap capacitor C1 (depicted in Figure 8) from charging from a voltage beyond the absolute maximum rating of the device when UVLO/EN is low (device is in shutdown). Additionally, if the temperature exceeds some limit, then the circuit is also turned off. Finally, REG5 may also be substituted by a 5V/18mA source while  $V_{CC}$  and PGND are used by the front end amplifier to increase the level of the ON/OFF voltage to sufficiently high for driving the MOSFET of the SMPS circuit ON/OFF. It is not necessary to include these in the SPICE model. The "70ns Blanking" is only used if CS is above the maximum current limit, when the transistor is driven ON, and the voltage added to the slope compensation goes rapidly to 0 to compensate for this overcurrent (when there is a '1' at the output of the Current Limit Comparator, then there is a '1' at the output of the OR gate, the Latch has a '1' in Set so its output Q goes to '1' fastly turning the NOR output to '0' starting the 70ns blanking. These functions were not included in the SPICE model.

# 5. Hardware Implementation

# 5.1. Hardware Design

As soon as the feasability and convergency of the system was established by the SPICE model (see section 4), the next was to design and build the real circuit. Using the MAX5068 datasheet specific components for the design were determined. A Microsoft EXCEL spreadsheet was used to facilitate easily changing values in order to explore the design space. Using a spreadsheet allowed all dependent values to be automatically calculated.

Table 1: Initial components calculation

| Ī                  | Table 1: Initial compo                                  | Theoretical Value | Actual Value      | Units |

|--------------------|---------------------------------------------------------|-------------------|-------------------|-------|

| f <sub>SW</sub>    | 10 <sup>11</sup> /4*R <sub>RT</sub>                     | 2,00E+05          | 2,08E+05          | Hz    |

| t <sub>DT</sub>    | 60*R <sub>DT</sub> [kΩ]/29.4                            | 7,96E+02          | 7,96E+02          | ns    |

| t <sub>RT</sub>    | 10*t <sub>SH</sub>                                      | 4,70E-02          | 4,70E-02          | S     |

| t <sub>sh</sub>    | . • • • • • • • • • • • • • • • • • • •                 | 4,70E-03          | 4,70E-03          | S     |

| T <sub>CLK</sub>   |                                                         | 5,00E+00          | 4,80E+00          | μs    |

| D                  |                                                         | 5,00E+01          | 5,00E+01          | %     |

| $T_{ON}$           | T <sub>CLK</sub> * D                                    | 2,50E+00          | 2,40E+00          | μs    |

| I <sub>FLINT</sub> | OLK                                                     | 6,00E+01          | 6,00E+01          | μA    |

| N <sub>S</sub>     |                                                         | 20                | 20                | turns |

| N <sub>P</sub>     |                                                         | 20                | 20                | turns |

| I <sub>PRI</sub>   | $I_{LOAD}*N_S/N_P$                                      | I <sub>LOAD</sub> | I <sub>LOAD</sub> | Α     |

| r                  | 20/18 0 1                                               | 4,00E-01          | 4,00E-01          |       |

| L                  | V <sub>ON</sub> *D/r*I <sub>LOAD</sub> *f <sub>SW</sub> | 25                | 25                | μH    |

| SR                 | 165*10-6/R <sub>RT</sub> *C <sub>SCOMP</sub>            | 2,00E+01          | 2,00E+01          | mV/s  |

| VREF               |                                                         | 1,23E+00          | 1,23E+00          | V     |

| VIN                |                                                         | 2,00E+01          | 20                | V     |

| VOUT               | (1 + R8/R9)*VREF                                        | 1,20E+01          | 1,58E+01          | V     |

| VON STARTUP        |                                                         | 1,00E+01          | 1,00E+01          | V     |

| VULR2              |                                                         | 1,23E+00          | 1,23E+00          |       |

| VON                | VIN - VOUT                                              | 8,00E+00          | 2,00E+01          | V     |

| C1                 |                                                         | 1,00E+00          | 1,00E+00          | μF    |

| CFLINT = C2        |                                                         | 1,00E-07          | 1,00E-07          | F     |

| CVCC = C3          |                                                         | 1,00E+00          | 1,00E+00          | μF    |

| CREG5 = C4         |                                                         | 1,00E-01          | 1,00E-01          | μF    |

| CSCOMP = C7        | 165*10-6/RRT*SR                                         | 6,60E-11          | 6,88E-11          | F     |

| C6                 |                                                         | NP                | NP                |       |

| R1                 |                                                         | 2,20E+02          | 2,20E+02          | kΩ    |

| RFLINT = R2        | tRT/0.595*CFLINT                                        | 7,90E+05          | 8,20E+05          | Ω     |

| RRT = R3           | 1011/4*fSW                                              | 1,25E+05          | 1,20E+05          | Ω     |

| RDT = R4           |                                                         | 3,90E+02          | 3,90E+02          | kΩ    |

| R5                 |                                                         | 3,90E+02          | 3,90E+02          | kΩ    |

| R6                 | (VON STARTUP/ VULR2 -1)*R7                              | 1,92E+02          | 1,80E+02          | Ω     |

| R7                 | ·                                                       | 2,20E+04          | 2,20E+04          | Ω     |

| R8                 | (VOUT/VREF - 1)*R9                                      | 1,93E+05          | 3,90E+05          | Ω     |

| R9                 | ·                                                       | 2,20E+04          | 3,30E+04          | Ω     |

| RCS                | 314[mV]/IPRI[mA]                                        | 5,00E-02          | 5,00E-02          | Ω     |

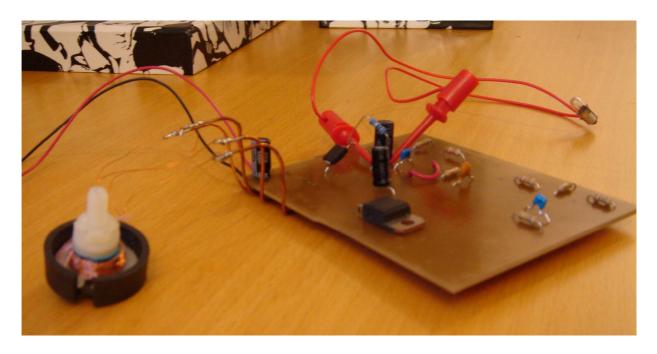

### 5.2. Hardware Construction

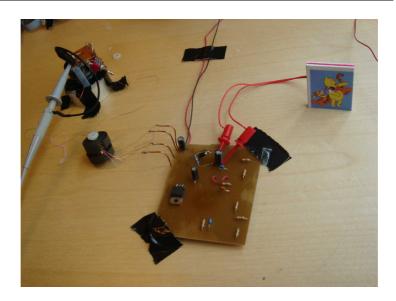

The final circuit was implemented as a circuit board. In order to do this implementation a number of tools were used, each of these is described below.

### - CAD Tools

OrCAD®Capture [31] was used for design capture and to generate a suitable NetList which was converted, with the help of OrCAD®Layout [32], into a single-sided circuit board to which all the components were soldered.

### - Design Capture

The initial circuit as captured is shown in

Figure 13. Some extra-components which appear as NP (Not Populated) were placed between strategical nodes, to simplify future modifications.

## - Layout

Figure 12 shows the bottom board view. Here the traces between components (red, indicating bottom layer), as well as their padstacks (the surface mounted devices padstacks on the bottom layer are shown in red; while the through hole padstacks on the top layer are shown in pale blue). Yellow marks the outline of the board, in order to separate this board from others which might be on the same panel.

Except for the MAX5068E and  $R_{CS}$ , all the remaining components are mounted through the board.

Figure 12: PCB footprint

### - Board Fabrication

Post processing of the layout files generates Gerber files which are used to fabricate the board (i.e., the spatial placement of the actual layout onto the circuit board material). These Gerber files are used by a circuit board milling machine [51] to create a single instance of the circuit board, by removing copper from places where there should not be connectivity. After the circuit board was milled and separated from the panel, then components were soldered on.

Figure 13: Initial Design

## 5.3. Hardware Refinements

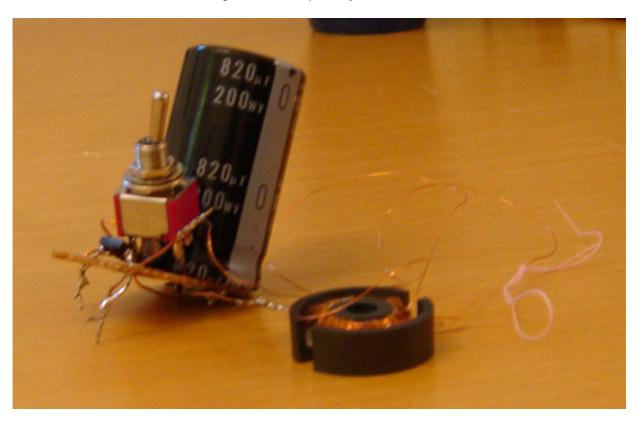

### 5.3.1. Initial Tests

The design previously described had some parts changed and some additions made in order to prevent the MAX5068 chip from being damaged. First, the supply voltage  $V_{\rm IN}$  was reduced from 20V to 12V while the transformer (primary and tertiary) was built by winding copper wire around a toroidal core (note that this toroid had not yet been split into to two physically separate parts) and the trace joining the node where the diode and R8 went into the IN pin was cut and a wire placed between the external DC source and the IN pin in order to make sure that the MAX5068 gets 12V DC to operate and the output regulated voltage value was decreased from roughly 16V to 9V by changing the values of R8 and R9 (they had been calculated to give 1.23V at FB pin when  $V_{\rm OUT}$  equaled roughly 16V, to give the desired new output voltage the parts were changed to: R8 = 220K; R9 = 33K in order to achieve  $V_{\rm OUT}$  = 9.4V). Finally, a load was connected to the diode, R8, and R9, consisting of a 47  $\mu$ F capacitor in parallel with a 12V bulb. This is to simulate a load and to have a visual output that things were working correctly.

The power source was then turned on, the voltages in some of the pins (REG5, VCC) had their expected values and the chip was not warm, FB had a dramatically low value, while (as it was logically expected) COMP was very high, indicating the absence of regulation at the output, however, Vout didn't reach the desired level.

## 5.3.2. Feedback from these initial tests, resulting design modifications

Some problems were detected and fixed. Each of these problems is described below along with the solution to this problem.

### Problem #1: NDRV pulse width

During testing it was observed that NDRV showed **too narrow pulses.** After examining the datasheet again it was seen that:

"When the voltage produced by the current at the primary side of the transformer (which also flows through the current-sense resistor) exceeds the current-limit comparator threshold, the MOSFET driver (NDRV) quickly terminates the current on-cycle. In most cases, a small RC filter is required to filter out the leading-edge spike on the sense waveform. Set the corner frequency to a few MHz above the switching frequency." [33]

Therefore an **RC filter**, which works as a low pass filter, widening these spikes into longer pulses was placed at pin NDRV to fix the problem:

- $f_{CORNER}$  = 3.78 MHz (above the 300 KHz desired operating  $f_{SW}$ )

- $R_{FILTER} = 1.2K\Omega$

- $C_{FILTER} = 220pF$

### Problem #2: FB path

The internal connection and behaviour of FB (linked to the error comparator) was unclear from the documentation, neither information about the input impedance nor about leakage currents or voltages were given on the datasheet. As a result of such an incomplete description from the vendor and, in order to ensure a voltage at the input of the error amplifier, in other words,  $V_{FB}$  that reflected what was happening at the *output* (47 $\mu$ F in parallel with 12V bulb) the values of R8 and R9 where reduced while an extra resistor was placed series with FB. Now, most of the current flowed through R8 and R9 while only voltage information was passed through FB. R5 was also modified to 1M, leading to a gain on the Error Amplifier (error AMP) of -17.8.

1M **R5 R8** 8.2K R9 2.2K **56K**  $R_{FB}$ DIGITAL 1.23V SOFT-START R8 **ERROR** AMP RFB FB current flow Low current R9 COMP

*Table 2: Modifications ensuring FB to receive a correct value*

Figure 14: New configuration for the FB path

$R_{FB}$  was added to provide a reasonable input resistance to the error amplifier, and R8/R9 were adjusted to have a much lower resistance so they would not be loaded down by the error amp. It was suspected that the previous higher resistances for R8, R9, and the absence of  $R_{FB}$  resulted in the input to the error amplifier being loaded down to the point where the output of the amplifier railed (i.e., swung to its power supply voltage) and stayed there preventing its proper operation.

### **Problem #3: Duty Cycle Limit**

As the output was not reaching a high enough voltage, in order to maximize the Duty Cycle, REG5 was shorted by using DT (this was done by removing R4 and replacing R14 by a wire).

### **Problem #4: Transformer Choice**

From the MAX5068 datasheet [33] it is known:

$$\frac{N_S}{N_P} \times \frac{K \times R_{CS} \times V_{OUT}}{L} = SR$$

(18)

For the initial design:

- K = 0.75

- $SR = 20 \text{mV}/\mu\text{A}$ ;

- $V_{OUT} = 12V$

- $R_{CS} = 0.05\Omega$

Where the slew rate, SR, is the slope of the sawtooth used to keep the system away from oscillations (commented in section 3.1.5. Internal Error Amplifier Therefore, since  $N_S$  =  $N_P$  was the initial test coniguration a value of **L** in the range of 20  $\mu$ H results from using equation 18. Even if that value does not need to be exactly the same as the transformer arm's equivalent inductance, it is a suitable starting reference point. Some toroid cores were removed from old power supplies (i.e., recycled). Unfortunately, there was no other available information than that they seem to be from AMIDON [34]. Fortunately, AMIDON gives specifications in their catalogue relating the dimensions of each toroid core with the number of turns around it to achieve a specific inductance. Hence the following procedure was used:

- 1. Measurements of the physical dimensions of the first core (inside diameter = 0.312; outside diameter = 0.500; height = 0.250), led to its identification as a **AMIDON FT-50A**.

- 2. Different numbers of turns were wound around it. Next, the inductance was measured with an RLC meter ¡Error! No se encuentra el origen de la referencia. working at 1kHz: Even if f<sub>SW</sub> is much higher (300 kHz) the number of turns hopefully will not need to be very high, so the difference in value of the parasitic capacitance between turns at different frequencies will be considered negligible.

These values were compared with the data given by the AMIDON catalog(see Table 3 and Figure 15) and deductions from these measurements were made.

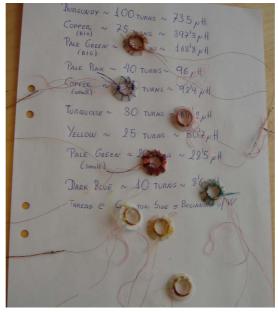

Figure 15: Graph comparing different materials and measured core behavior

| Table 3: Comparing | different i | materials                             | (values | from   | [341)   | ) and  | measured       | core behavior      |

|--------------------|-------------|---------------------------------------|---------|--------|---------|--------|----------------|--------------------|

| Twee or Companies  | city citt   | i i i i i i i i i i i i i i i i i i i | (Curre  | 110111 | 1 - 1 / | viiivi | THE COLOUR COL | core certification |

| Turns | Measured<br>[µH] | Material #61<br>[µH] | Material #67 [μH] | Material #68 [µH] |

|-------|------------------|----------------------|-------------------|-------------------|

| 50    | 99,6             | 186                  | 60                | 28                |

| 40    | 67,9             | 120                  | 38                | 18                |

| 30    | 42,6             | 68                   | 33                | 10                |

| 20    | 22,2             | 30                   | 20                | 4                 |

| 10    | 8,6              | 8                    | 2                 | 1                 |

None of the values fit with what was given in the catalog, but a closer look at the graph shows that the measured material is something intermediate between materials #61 and #67. So even if the values relating inductance with turns are not given in the catalog, **material** #64 [34] has a  $\mu_{64\_MAX}$  = 375; intermediate between  $\mu_{67\_MAX}$  = 125 and  $\mu_{61\_MAX}$  = 450. Therefore, our hypothesis is that the toroid was made of material #64.

- 3. 20 turns of wire were wound around the initial toroid core, giving a  $L \approx 25\mu H$ ; this was repeated to form both the primary and tertiary coils. Measurements of this configuration were used to check the convergency and stability of the system.

- 4. This test was **successful** with the voltage at the output regulated to 9V

Following the above test, a number of subsequent tests were made with other bigger toroids whose  $\mu$  was determined to be much higher (estimated to be in the range of "material J"[34] or higher). Nevertheless, measurements revealed that in order to achieve a suitable L value

(within the range of 20-30  $\mu H$  for the Primary and Tertiary as needed in order to keep the MAX5068 within regulation and avoiding problems with this chip) the number of turns should be very few, because a single turn led to 25  $\mu H$  of measured inductance, while two turns produced 55  $\mu H$ . Analysis of data from this trial showed that even if L has the same value, too few turns on the coil ruins the energy transfer by the transformer (i.e., between the primary and the secondary) so the voltage never rose to suitable levels with these cores. We would have predicted (using Faraday's law) that the emf would be proportion to the number of turns [35] and also because we know from equation 6 that the flux density, B, is directly proportional to the number of turns:

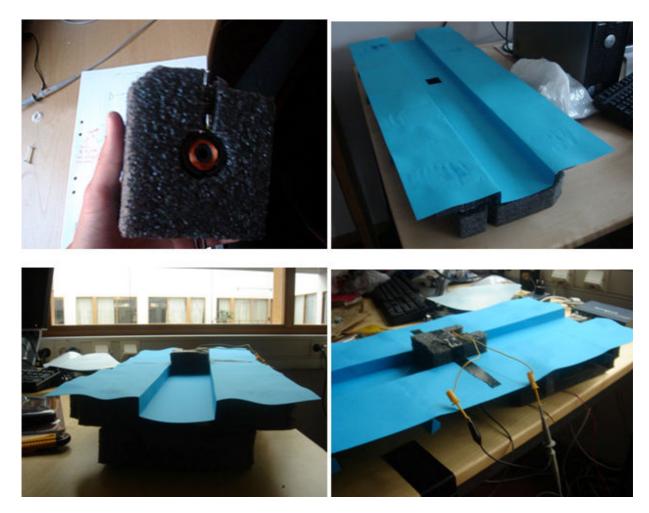

$$emf \propto N_{TURNS}$$

(19)