# Performance and Power-Consumption Implication of Fine-Grained Synchronization in Multiprocessors

A Master of Science Thesis in Computer Systems by Oscar Sierra Merino

Department of Microelectronics and Information Technology

Royal Institute of Technology

Stockholm – May 2.002

## **Abstract**

It has been already verified that hardware-supported fine-grain synchronization provides a significant performance improvement over coarse-grained synchronization mechanisms, such as barriers. Support for fine-grain synchronization on individual data items becomes notably important in order to implement thread-level parallelism more efficiently.

One of the major goals of this project is to propose a new efficient way to support fine-grain synchronization mechanisms in multiprocessors. This novel idea is based on the efficient combination of fine-grain synchronization with cache coherence and instruction level parallelism. Both snoopy and directory-based cache coherence protocols have been studied.

The work includes the definition of the complete set of synchronizing memory instructions as well as the architecture of the full/empty tagged shared memory that provides support for these operations.

A detailed model based on a shared memory multiprocessor is presented and systematically described. To achieve this, an existing execution-driven simulator, namely RSIM, has been appropriately adapted. The simulation environment is designed for verification and performance evaluation of the proposed solutions.

Some guidelines for implementing a power estimation algorithm as an extended feature of the simulation platform have been presented. The integration of fine-grain synchronization at the cache coherence level is expected to increase the energy consumption of the system.

**Keywords**: fine-grain synchronization, shared memory, instruction-level parallelism, cache coherence, power consumption, execution-driven simulation.

## **Table of Contents**

| 1. | Overviev    | v and motivation                                             | 8  |

|----|-------------|--------------------------------------------------------------|----|

| 2. | Semantic    | es of synchronizing memory operations                        | 9  |

| 3. | Architec    | tural support for fine-grain synchronization                 | 11 |

|    | 3.1. Rela   | ted work                                                     | 11 |

|    | 3.1.1.      | The Alewife machine                                          | 11 |

|    | 3.1.2.      | The StarT-NG machine                                         | 12 |

|    | 3.2. Prop   | osed architecture                                            | 14 |

|    | 3.3. Cach   | e coherence                                                  | 17 |

| 4. | Integration | on with snoopy protocols                                     | 19 |

|    | 4.1. Map    | ping between processor instructions and bus transactions     | 23 |

|    | 4.2. Man    | agement of pending requests                                  | 25 |

|    | 4.3. Tran   | sition rules.                                                | 27 |

|    | 4.3.1.      | Invalid state                                                | 27 |

|    | 4.3.2.      | Modified state                                               | 28 |

|    | 4.3.3.      | Exclusive-clean state                                        | 29 |

|    | 4.3.4.      | Shared state                                                 | 30 |

|    | 4.4. Sum    | mary                                                         | 30 |

| 5. | Integration | on with directory-based protocols                            | 32 |

|    | 5.1. Map    | ping between processor instructions and network transactions | 34 |

|    | 5.2. Man    | agement of pending requests                                  | 36 |

|    | 5.3. Direc  | ctory transition rules                                       | 38 |

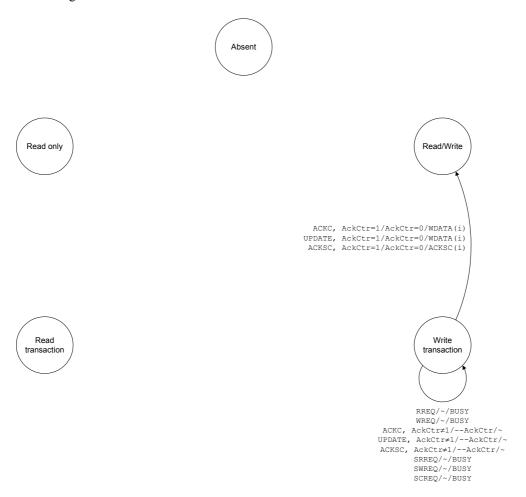

|    | 5.3.1.      | Absent state                                                 | 38 |

|    | 5.3.2.      | Read-only state                                              | 39 |

|    | 5.3.3.      | Read-write state                                             | 41 |

|    | 5.3.4.      | Read transaction state                                       | 43 |

|    | 5 3 5       | Write transaction state                                      | 44 |

| 5.4. Summary                                             | 46 |

|----------------------------------------------------------|----|

| 6. Simulation framework                                  | 47 |

| 6.1. Features of the simulated platform                  | 47 |

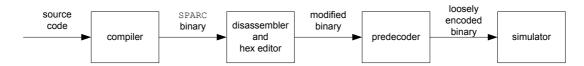

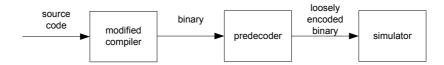

| 6.2. Simulation methodology                              | 48 |

| 6.3. Implementation of synchronizing instructions        | 49 |

| 6.4. Simulation flowchart                                | 52 |

| 6.5. Simulation results                                  | 54 |

| 7. Power-consumption estimation                          | 57 |

| 7.1. Available energy estimation tools                   | 57 |

| 7.2. Implementing an energy estimation framework in RSIM | 58 |

| 7.3. Planned experiments                                 | 59 |

| 8. Conclusions                                           | 60 |

| 9. Future work                                           | 61 |

| Appendix A. Preparing binaries for simulation            | 62 |

| Appendix B. Application source (fine-grained version)    | 64 |

| Appendix C. Application source (coarse-grained version)  | 66 |

| Acknowledgements                                         | 68 |

| References                                               | 69 |

## List of Figures

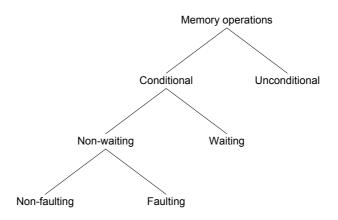

| Figure 1: Classification of synchronizing operations (extracted from [72])                       | 9  |

|--------------------------------------------------------------------------------------------------|----|

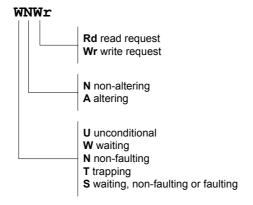

| Figure 2: Notation of synchronizing memory operations                                            | 10 |

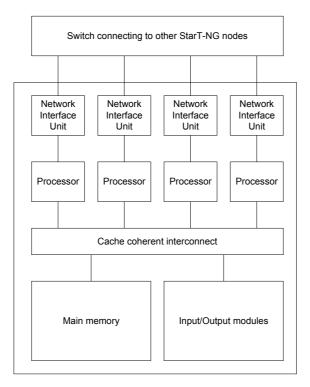

| Figure 3: Architecture of a StarT-NG node [27]                                                   | 12 |

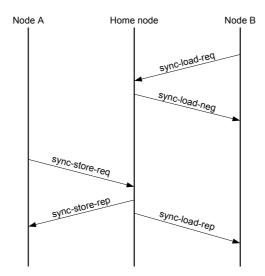

| Figure 4: Two sample scenarios of synchronized loads and stores                                  | 13 |

| Figure 5: Logical structure of shared memory                                                     | 14 |

| Figure 6: Memory map for each processing node                                                    | 15 |

| Figure 7: Organization of a cache supporting fine-grain synchronization                          | 15 |

| Figure 8: Cache line containing both ordinary and synchronized data                              | 16 |

| Figure 9: Bus-based system architecture                                                          | 19 |

| Figure 10: MESI coherence protocol                                                               | 20 |

| Figure 11: MESI protocol integrated with fine-grain synchronization (explicit full/empty states) | 21 |

| Figure 12: MESI protocol integrated with fine-grain synchronization (implicit full/empty states) | 22 |

| Figure 13: Sample scenario of mapping between processor instructions and bus transactions        | 24 |

| Figure 14: Resuming of pending requests                                                          | 26 |

| Figure 15: Mesh network-based architecture                                                       | 32 |

| Figure 16: Alewife's coherence protocol state diagram                                            | 32 |

| Figure 17: Management of pending requests for an absent or read-only memory block                | 36 |

| Figure 18: Management of pending requests for a read-write memory block                          | 37 |

| Figure 19: State transitions from the absent state                                               | 39 |

| Figure 20: State transitions from the read-only state                                            | 41 |

| Figure 21: State transitions from the read-write state                                           | 43 |

| Figure 22: State transitions from the read transaction state                                     | 44 |

| Figure 23: State transitions from the write transaction state                                    | 45 |

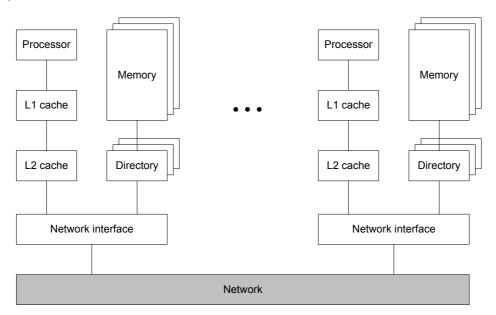

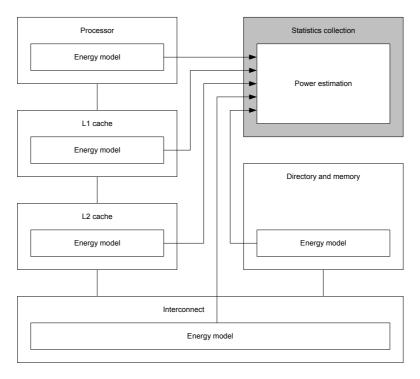

| Figure 24: Simulated system architecture                                                         | 47 |

| Figure 25: Simulation steps                                                                      | 48 |

| Figure 26: Simulation steps with a compiler supporting synchronizing instructions                | 49 |

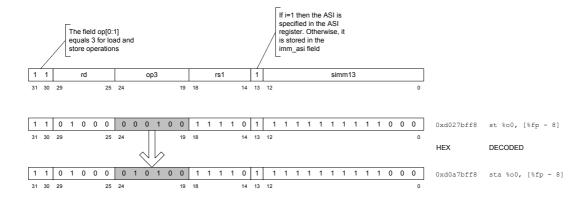

| Figure 27: Alternate load and store instruction format                                           | 49 |

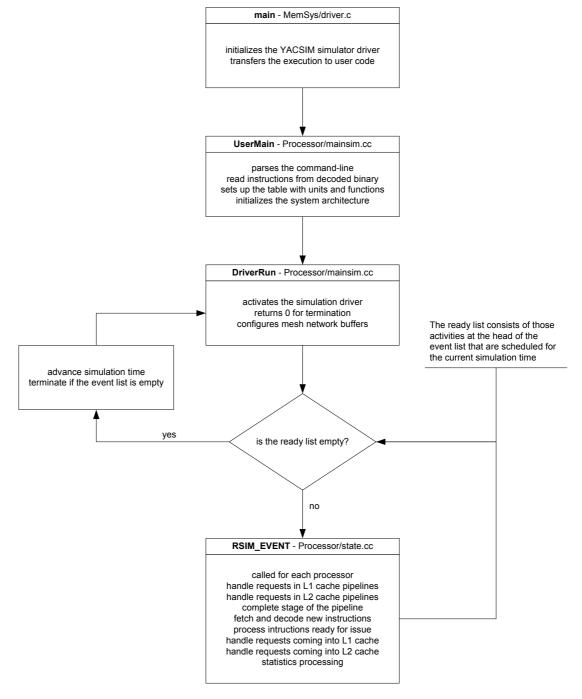

| Figure 28: Execution flowchart of the simulator                                                  | 52 |

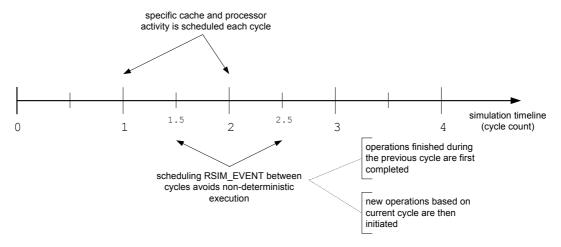

| Figure 29: RSIM_EVENT scheduling                                                | 53 |

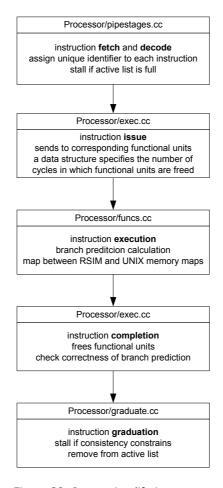

|---------------------------------------------------------------------------------|----|

| Figure 30: Instruction lifetime stages                                          | 53 |

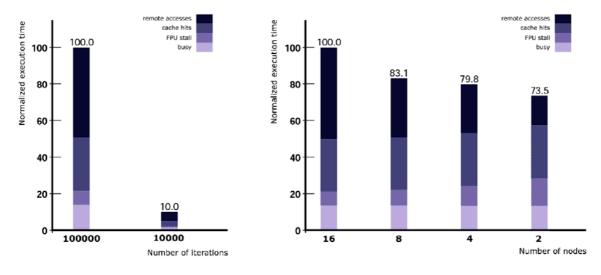

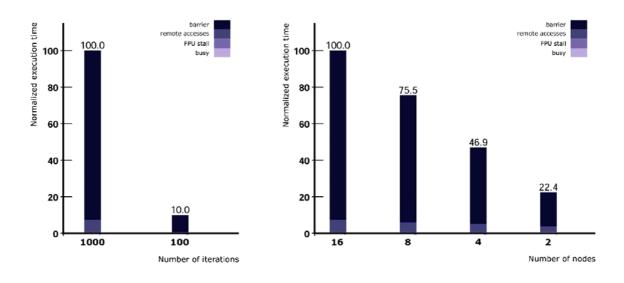

| Figure 31: Normalized execution time for different machine and problem sizes    | 54 |

| Figure 32: Integrated power consumption framework                               | 59 |

| Figure 33: Details on how to transform a standard store to a synchronized store | 63 |

## List of Tables

| Table 1: Notation of synchronized operations                               | 10 |

|----------------------------------------------------------------------------|----|

| Table 2: Relevant information stored in ordinary MSHR registers [46]       | 16 |

| Table 3: Additional bus transactions in the MESI protocol                  | 22 |

| Table 4: Correspondence between processor instructions and memory requests | 23 |

| Table 5: Management of coalescing requests                                 | 25 |

| Table 6: Semantics of the transitions in the directory-based protocol      | 33 |

| Table 7: Network transactions in the directory-based protocol              | 35 |

| Table 8: Correspondence between processor instructions and memory requests | 35 |

| Table 9: ASI values for synchronizing operations.                          | 50 |

| Table 10: Specific modifications made to RSIM                              | 50 |

| Table 11: Set of full/empty memory instructions                            | 51 |

| Table 12: Execution times (in cycles) for 1.000 iterations                 | 55 |

| Table 13: Execution times (in cycles) for 16 nodes                         | 55 |

| Table 14: Structure of switch capacitance tables                           | 58 |

| Table 15: Relevant values of the op3 field                                 | 63 |

## 1. Overview and motivation

Two types of synchronization operations guarantee correctness in shared-memory multiprocessors: mutual exclusion and conditional synchronization, such as producer-consumer data dependency. Barriers are an example of synchronization directives that ensure the correctness of a producer-consumer behavior. They are coarse-grain in the sense that all processes have to wait in a common point before they can proceed, even though the data they truly depend on was available in a previous execution step.

The main advantage of fine-grain synchronization arises from the fact that synchronization is provided at data-level. As a consequence, false data dependencies and unnecessary process waiting are avoided. Communication overhead due to global barriers is also avoided, because each process communicates only with the processes it depends on. Thus, the serialization of program execution is notably reduced and more parallelism can be exploited. This effect is more noteworthy as the number of processors increases. While the overhead of a fine-grain synchronization operation remains constant, that of a coarse-grain operation typically increases with the number of processors.

As explained in [78], fine-grain synchronization is most commonly provided by three different mechanisms:

- i) language-level support for expressing data-level synchronization operations,

- ii) full/empty bits storing the synchronization state of each memory word,

- iii) processor operations on full/empty bits.

Traditional theory on data-level parallelism has led to the definition of specific structures supporting fine-grain synchronization in data arrays. As an example, J-structures provide consumer-producer style of synchronization, while L-structures guarantee mutual exclusion access to a data element [4]. Both data types associate a state bit with each element of an array.

Several alternatives exist for handling a synchronization failure. The most immediate are either polling the memory location until the synchronization condition is met or blocking the thread and returning the control at a later stage, which requires more support as it is necessary to save and restore context information. A combination of both is another option, polling first for a given period and then blocking the thread. The waiting algorithm may depend on the type of synchronization being executed [52].

Most research regarding multiprocessors show that fine-grain synchronization is a valuable alternative for improving the performance of many applications. As exposed in [46], evidence is shown on the worthiness of having modest hardware support for fine-grain synchronization. Testing the benefits of aggressive hardware support in fine-grain synchronization is one of the goals of this project.

## 2. Semantics of synchronizing memory operations

Synchronization operations require the use of a *tagged* memory, in which each location is associated to a state bit in addition to a 32-bit value. The state bit is known as *full/empty* bit and implements the semantics of synchronizing memory accesses. As a matter of fact, this bit controls the behavior of synchronized loads and stores. A set *full/empty* bit indicates that the corresponding memory reference has been written by a successful synchronized store. On the contrary, an unset *full/empty* bit means either that the memory location has never been written since it was initialized or that a synchronized load has read it.

A complete categorization of the different synchronizing memory operations is depicted in Figure 1. These instructions are introduced as an extension of the instruction set of *Sparcle* [6], which is in turn based on SPARC. The simplest type of operations includes *unconditional* load, *unconditional* store, setting the *full/empty* bit or a combination of these. As they do not depend on the previous value of the *full/empty* bit, *unconditional* operations always succeed.

Figure 1: Classification of synchronizing operations (extracted from [72])

Conditional operations depend on the value of the full/empty state bit to successfully complete. A conditional read, for instance, is only performed if the state bit of the location being accessed it set. The complimentary applies for a conditional write. Conditional memory operations can be either waiting or non-waiting. In the former case, the operation remains pending in the memory until the state miss is resolved. This introduces non-deterministic latencies in the execution of synchronizing memory operations. Lastly, conditional non-waiting operations can be either faulting or non-faulting. While the latter do not treat the miss as an error, faulting operations fire a trap on a state miss and either retry the operation immediately or switch to another context.

Figure 2: Notation of synchronizing memory operations

All memory operations, regardless of the classification made in Figure 1, can be further catalogued into *altering* and *non-altering* operations. While the former modify the *full/empty* bit after a successful synchronizing event, the latter do not touch this bit in any case. According to this distinction, ordinary memory operations fall into the *unconditional non-altering* category.

The following table shows the notation used for each variant of memory operation and its behavior in the case of a synchronization miss. The notation is further explained in Figure 2.

Notation Semantics Rehavior on a synchronization miss UNRd Unconditional non-altering read UNWr Unconditional non-altering write Never miss UARd Unconditional altering read UAWr Unconditional altering write WNRd Waiting and non-altering read from full WNWr Waiting and non-altering write to empty Placed on the list of pending requests until resolved WARd Waiting and altering read from full WAWr Waiting and altering write to empty NNRd Non-faulting and non-altering read from full NNWr Non-faulting and non-altering write to empty Silently discarded NARd Non-faulting and altering read from *full* NAWr Non-faulting and altering write to *empty* TNRd Faulting and non-altering read from full TNWr Faulting and non-altering write to *empty* Signal trap TARd Faulting and altering read from full TAWr Faulting and altering write from empty

Table 1: Notation of synchronized operations

## 3. Architectural support for fine-grain synchronization

#### 3.1. Related work

#### 3.1.1. The Alewife machine

The MIT Alewife machine is a cache-coherent shared memory multiprocessor (see [2] and [4]) with non-uniform memory access (NUMA). Although it is internally implemented with an efficient message-passing mechanism, it provides an abstraction of a global shared memory to programmers. The most relevant part of its nodes regarding coherency and synchronization protocols is the communication and memory management unit (CMMU), which deals with memory requests from the processor and determines whether a remote access is needed, managing also cache fills and replacements. Cache coherency is achieved through LimitLESS, a software extended directory-based protocol. The home node of a memory line is responsible for the coordination of all coherence operations for that line.

Support for fine-grain synchronization in Alewife includes full/empty bits for each 32-bit data word and fast user-level messages. Colored load and store instructions are used to access synchronization bits. The *alternate space indicator* (ASI) distinguishes each of these instructions. Full/empty bits are stored in the bottom four bits of the coherency directory entry (at the memory) and as an extra field in the cache tags (at the cache), so they do not affect DRAM architecture nor network data widths. The Alewife architecture also defines language extensions to support both J- and L-structures. A specific programming language, namely Semi-C<sup>1</sup>, has been defined for this purpose [42].

The aim is that a successful synchronization operation does not incur much overhead with respect to a normal load or store. In the ideal case, the cost of both types of operations is expected to be the same. This is possible because full/empty bits can be accessed simultaneously with the data they refer to. The cost of a failed synchronization operation depends much on the specific hardware support for synchronization. The overhead of software-supported synchronization operations is expected to be much higher than their hardware counterparts. However, Alewife minimizes this by rapidly switching between threads on a failed synchronization attempt or a cache miss, requiring the use of lockup-free caches.

Handling failed synchronization operations in software has the advantage of being less complex in terms of hardware and more flexible. The basis of Alewife support for fine-grain synchronization is that, as synchronization operations are most probably successful, overhead due to such failures is not expected to notably reduce overall system performance.

11

<sup>&</sup>lt;sup>1</sup> Semi-C is an extension of the C language that can handle parallel programming constructs.

#### 3.1.2. The StarT-NG machine

StarT-NG, an improved version of the StarT machine [9], is a high-performance *message* passing architecture in which each node consists of a commercial symmetric multiprocessor (SMP) that can be configured with up to 3 processors, which are connected to the main memory by a data crossbar. At least one *network interface unit* is present in each node, allowing communicating with a *network router*, which is implemented in a proprietary chip [17].

A low-latency high-bandwidth network interconnects every node in the system. StarT-NG also supports cache-coherent global shared memory. In this case, one processor on each site is used to implement the shared memory model. This functionality can be disabled when shared memory is not needed.

Figure 3: Architecture of a StarT-NG node [27]

Coherence protocols in StarT-NG are fully implemented in software. As a consequence, the choice of protocols and configuration of the shared memory is notably flexible. The performance of several coherence models has been evaluated. Particularly relevant to this work is the study made in [75], which introduces a cache coherence protocol with support for fine-grained data structures. These data structures are known as I-structures [75].

According to the results of this study, performance improvements in an integrated coherence protocol are two-fold. First, the write-once behavior of I-structures allows writes to be performed without the exclusive ownership of the respective cache line. Once a write has been carried out, stale data in other caches is identified because its *full/empty* bit is unset. In a *directory-based* protocol, a synchronized load in a remote location will find the *full/empty* bit

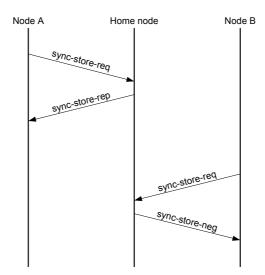

unset and forward the request to the proper node. This behavior is illustrated in Figure 4, where two nodes (namely, A and B) share a copy of a block on which they perform different operations.

Scenario 1 Initially, both nodes A and B have a copy of the cache line in the shared state. A synchronized store operation is performed by node A without the *exclusive ownership* of the cache block, which is consequently kept in the *shared* state during the whole process. Pending synchronized loads from node B to the affected slot are resumed after the store is performed.

Scenario 2 Initially, both nodes A and B have a copy of the cache line in the shared state. A synchronized store operation is successfuly performed by node A without the exclusive ownership of the cache block. If node B issues a synchronized store, the request will be rejected by the home node after finding the full-empty bit set.

Figure 4: Two sample scenarios of synchronized loads and stores

As stated in [74], another advantage of a coherence protocol integrated with fine-grain synchronization is the efficiency in the management of pending requests by reducing the number of transactions needed to perform some particular operations. As an example, a synchronized

load in traditional coherence protocols usually requires the requesting node to obtain the exclusive ownership of the affected block in order to set the *full/empty* bit to the empty state.

## 3.2. Proposed architecture

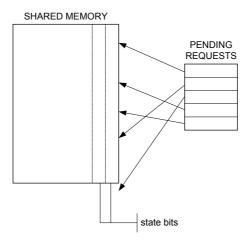

In a multiprocessor system providing fine-grain synchronization, each shared memory word is tagged with a full/empty bit that indicates the synchronization state of the referred memory location. Assuming that a memory word is 32-bit long, this implies an overhead of just 3%. Although many variations exist when implementing this in hardware, the structure of shared memory is conceptually as shown in Figure 5.

Figure 5: Logical structure of shared memory

Figure 5 shows that each shared memory location has three logical parts, namely:

- i) the shared data itself.

- ii) *state* bits. The *full/empty* bit is placed within the *state* bits. This bit is set to 1 if the corresponding memory location has already been written by a processor and thus contains valid data. If the architecture has cache support other *state* bits such as the *dirty* bit may exist. The *dirty* bit is set if the memory location is not up-to-date, indicating that it has been modified in a remote node.

- iii) the list of pending memory requests. Synchronization misses fired by conditional waiting memory operations are placed in this list. When an appropriate synchronizing operation is performed, the relevant pending requests stored in this list are resumed. If the architecture has cache support, the list of pending memory requests also stores ordinary cache misses. The difference between both types of misses is basically that synchronization misses store additional information, such as the accessed slot's index in the corresponding cache block. These differences are further explained later in this section.

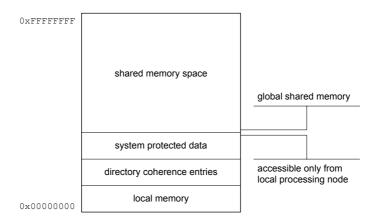

Note that fine-grain synchronization is described here only for shared memory locations. In the presented architecture, the local memory in each processing node does not make use of *full/empty* bits. With this consideration, the memory map of the system seen by each processor is similar to the one sketched in Figure 6.

Figure 6: Memory map for each processing node

Fine-grain synchronization is implemented by atomic test-and-set operations. These operations modify the *full/empty* condition bit in the processor's condition bits register<sup>2</sup>. Note that the condition bit is changed regardless of the particular variant of synchronization operation; no matter it is altering and/or trapping.

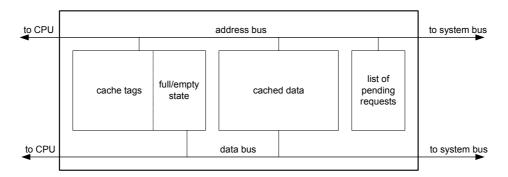

As stated before, many implementation alternatives are possible. State bits may be stored in the coherence directory entry in the case of a *directory-based* protocol, such as the one implemented in Alewife. A proposed structure for a cache supporting *fine-grain* synchronization is depicted in Figure 7.

Figure 7: Organization of a cache supporting fine-grain synchronization

When a memory word is cached, its *full/empty* bit must also be stored at the cache side. As a consequence, not only data has to be kept coherent, but also *full/empty* bits. In a system with cache support, an efficient option is to store the *full/empty* bit as an extra field in the cache tag, allowing checking the synchronization state in the same step as the cache lookup. The coherence protocol has then two logical parts, one for the data and another for the synchronization bit.

<sup>&</sup>lt;sup>2</sup> In *Sparcle*, for instance, the full/empty condition bit is stored in the condition bit #0 (see [73]).

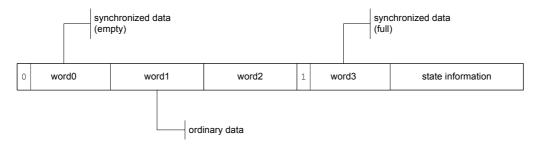

Our design assumes that the smallest synchronizing element is a word. As a cache line is usually longer, it may contain multiple elements, including both synchronized and ordinary data (see Figure 8). A tag for a cache line includes the *full/empty* bits for all the synchronized words that are stored in that line. As directory states are maintained at cache line level, this complicates the maintenance of pending memory requests. Effectively, while a *dirty* bit refers to a complete cache line, a *full/empty* bit refers to a single word in a cache line.

Figure 8: Cache line containing both ordinary and synchronized data

In the proposed architecture, lists of pending requests are maintained in hardware at the cache level, more concretely in the *miss status holding registers* (MSHR). With this assumption, waiting memory operations require the architecture to have cache support. However, if cache support is not available, the behavior of waiting operations can be implemented in software by using faulting conditional operations instead. The system kernel is then responsible for maintaining the list of pending requests [39]. In the case of a *directory-based* coherence protocol, an alternative is to store the pending requests as a separate field in the directory entries.

Some modifications have to be made to the cache architecture in case synchronization misses are to be kept in MSHR. More concretely, MSHR in traditional *lockup-free* caches store the information listed in Table 2 (see [46] for a more detailed description). In order to store synchronization misses in these registers, two more fields have to be added containing the slot's index accessed by the operation and the specific variant of synchronized operation that will be performed.

| Field                 | Semantics                                                 |

|-----------------------|-----------------------------------------------------------|

| Cache buffer address  | Location where data retrieved from memory is stored       |

| Input request address | Address of the requested data in main memory              |

| Identification tags   | Each request is marked with a unique identification label |

| Send-to-CPU flags     | If set, returning memory data is sent to CPU              |

| In-input stack        | Data can be directly read from input stack if indicated   |

| Number of blocks      | Number of received words for a block                      |

| Valid flag            | When all words have been received the register is freed   |

| Obsolete flag         | Data is not valid for cache update, so it is disposed     |

Table 2: Relevant information stored in ordinary MSHR registers [46]

A complete description of a cache coherence mechanism includes the states, the transition rules, the protocol message specification and the description of cache line organization and memory management of pending requests. Other design issues are dealing with conflicting and/or merging synchronization misses, as well as ordering of misses from the same processor.

Our design is based on a multiprocessor system with the following assumptions:

- the CPU implements *out-of-order* execution of instructions,

- each processing node has a *miss-under-miss lockup-free* cache, supporting multiple outstanding memory requests,

- the smallest synchronized data element is a word; this statement does not imply a loss of generality, as the extension of the presented design to other data sizes is straightforward.

### 3.3. Cache coherence

In a multiprocessor system, cache memory local to each processing node can be used to speed up memory operations. It is necessary to keep the caches in a state of coherence by ensuring that modifications to data that is resident in a cache are seen in the rest of the nodes that share a copy of the data. This can be achieved in several ways, which may depend on the particular system architecture. In bus-based systems, for instance, cache coherence is implemented by a snooping mechanism, where each cache is continuously monitoring the system bus and updating its state according to the relevant transactions seen on the bus. On the contrary, mesh network-based multiprocessors use a directory structure to ensure cache coherence. In these systems, each location in the shared memory is associated with a directory entry that keeps track of the caches that have a copy of the referred location. Both *snoopy* and *directory-based* mechanisms can be further classified into *invalidation* and *update* protocols. In the former case, when a cache modifies shared data, all other copies are set as invalid. Update protocols change copies in all caches to the new value instead of marking them as invalid.

The performance of multiprocessor systems is partially limited by cache misses and node interconnection traffic. Consequently, cache coherence mechanisms play an important role in solving the problems associated with shared data. Another performance issue is the overhead imposed by synchronizing data operations. In the case of systems that provide fine-grain synchronization, this overhead is due to the fact that synchronization is implemented as a separate layer over the cache coherence protocol. Indeed, bandwidth demand can be reduced if no data is sent in a synchronization miss. This behavior requires the integration of cache coherence and fine-grain synchronization mechanisms. It is important to remark, however, that both mechanisms are conceptually independent. This means that synchronizing operations can be implemented in machines without cache support and vice-versa.

One of the main objectives of this project is to define a coherence protocol that integrates fine-grain synchronization. This will be done for both *snoopy* and *directory-based* protocols. An event-driven simulator, namely RSIM, is used in order to verify and measure the performance of our design. As this simulation platform does not integrate synchronization at the cache coherence level, modifications in its source code are needed.

In the proposed architecture, failing synchronizing events are resolved in hardware. The following architecture requirements must be considered in order to integrate synchronization and cache coherency. Note that most of the hardware needed is usually already available in modern multiprocessor systems.

- i) each memory word has to be associated with a full/empty bit; as in Alewife, this state information can be stored in the coherency directory entry,

- at the cache side, state information is stored as an additional field in the cache tags; a lookup-free cache is needed in order to allow non-blocking loads and stores,

- iii) the cache controller not only has to deal with coherency misses, but also with full/empty state misses; synchronization is thus integrated with cache coherency operations, as opposed to Alewife, in which the synchronization protocol is implemented separately from the cache coherency system.

This approach can be extended to the processor registers by adding a full/empty tag to them. This would allow an efficient execution of synchronization operations from simultaneous threads on the registers. However, additional modifications are needed in the processor architecture to implement this feature.

In order to evaluate the performance improvement of this novel architecture with respect to existing approaches, appropriate workloads must be tested on the devised machine. A challenge task is to find suitable applications that show these results in a meaningful way, so that the effects of the synchronization overhead such as the cost of additional state storage, execution latency or extra network traffic can be studied in detail.

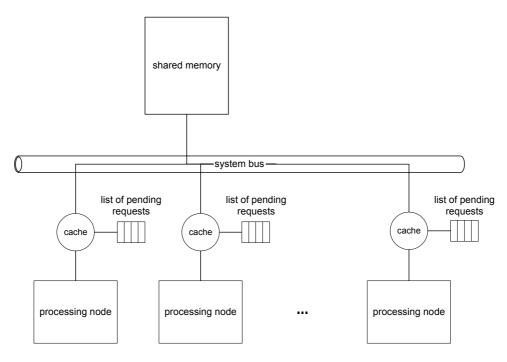

## 4. Integration with snoopy protocols

Figure 9: Bus-based system architecture

We consider a bus-based system such that depicted in Figure 9. Note that even though each memory address has conceptually a list of pending operations for that address, at hardware level the lists are distributed between all the processing nodes. The management of deferred lists will be explained later in this section. The description made here is based on the MESI protocol, also known as Illinois protocol. It is a four-state write-back invalidation protocol with the following state semantics [30]:

- modified this cache has the only valid copy of the block; the location in main memory is invalid.

- exclusive clean this is the only cache that has a copy of the block; the copy in main memory is up-to-date. A signal S is available to the controller in order to determine on a BusRd if any other cache currently holds the data.

- shared the block is present in an unmodified state in this cache, main memory is up-todate and zero or more caches may also have a shared copy.

- invalid the block does not have valid data.

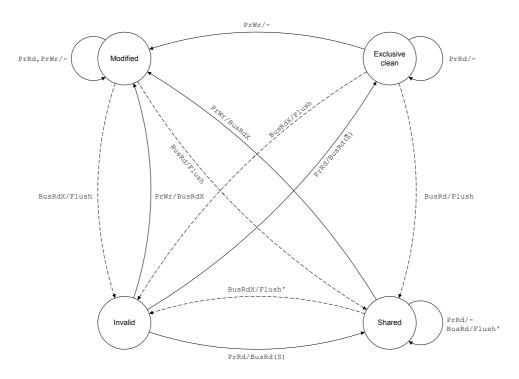

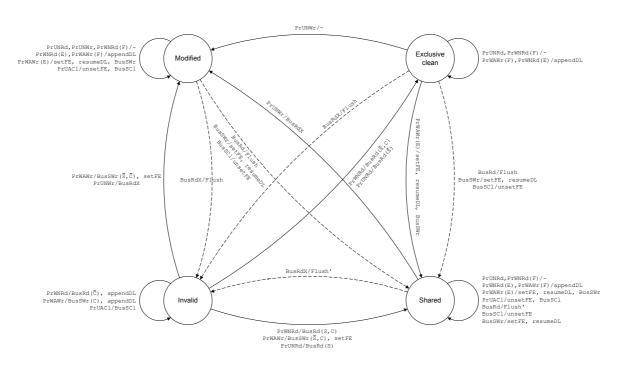

The state diagram corresponding to the MESI protocol without fine-grain synchronization support is shown in Figure 10.

Figure 10: MESI coherence protocol

In the figure above, we use the notation A/B, where A indicates an observed event and B is an event generated as a consequence of A. Dashed lines show state transitions due to observed bus transactions, while continuous lines indicate state transitions due to local processor actions. Finally, the notation Flush' means that data is supplied only by the corresponding cache. Note that this diagram does not consider transient states used for bus acquisition.

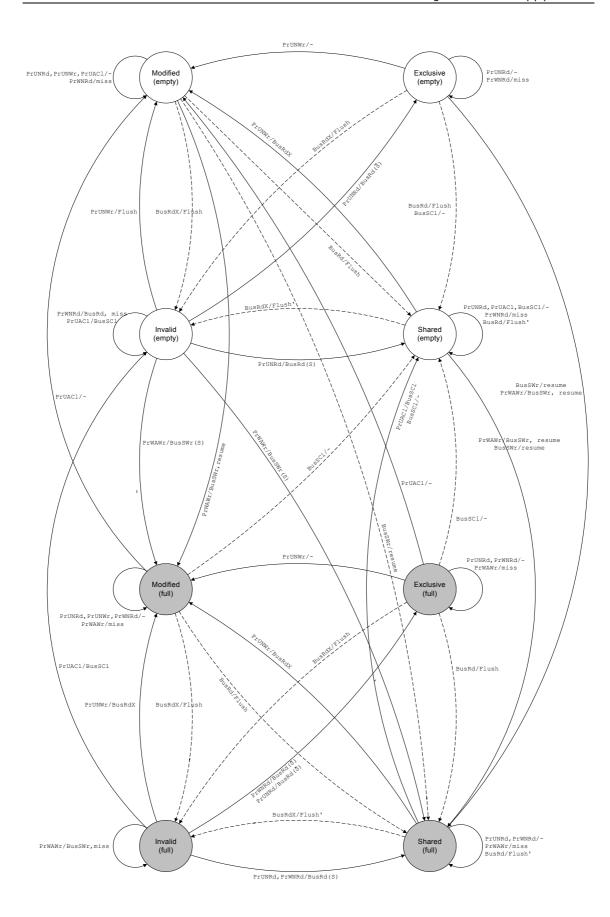

The transitions needed to integrate fine-grain synchronization in MESI are sketched in Figure 11, in which the *full/empty* state of the accessed word is explicitly indicated by splitting the ordinary MESI sates into two groups. The transactions not shown in this figure are not relevant for the corresponding state and do not cause any transition in the receiving node. The notation is the same as in the previous figure, and as it can be appreciated below, no new states are preliminarily required so as to integrate fine-grain synchronization in the coherence protocol.

The description made here considers only waiting non-altering reads and waiting altering writes. Altering reads can be achieved by issuing non-altering reads in combination with an operation that clears the *full/empty* bit without retrieving data. This operation is named *unconditional altering clear*, or Pruacl according to the nomenclature previously described. Pruacl operates on a *full/empty* bit without accessing or altering the data corresponding to that state bit.

Clearing of *full/empty* bits is necessary in order to reuse synchronized memory locations (a more detailed description is made in [46]). While a Pruard could be used for this end, the Pruard instruction completes faster, as it alters the *full/empty* bit without actually reading data from the corresponding location. For this reason, Pruard can be seen as an optimized memory instruction.

Figure 11: MESI protocol integrated with fine-grain synchronization (explicit full/empty states)

Waiting operations constitute the most complex sort of synchronizing operations, as they require additional hardware in order to manage deferred list and resume pending synchronization requests. The behaviour of other types of memory operations is a simplified version of waiting operations. Most of the transitions depicted in Figure 11 are identical in the rest of the cases, with the only different being the behaviour when a synchronization miss is detected. Instead of being added to the list of pending requests, other variants of missing operations either fire an exception or are silently discarded.

Two additional bus transactions are needed in order to integrate fine-grain synchronization in the MESI protocol. A detailed description of these bus transactions is presented in Table 3. Coherence of *full/empty* bits is ensured precisely by these two bus transactions (BusSWr and BusSC1).

| Bus<br>transaction | Description                                                                                                                                                                                                                                                                      |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BusSWr             | A node has performed an altering waiting write. The effect of this operation in observing nodes is to set the <i>full/empty</i> bit of the referring memory location and resume the relevant pending requests. Resuming of pending requests is further explained in section 4.2. |

| BusSCl             | A node has performed an <i>altering read</i> or an <i>unconditional clear</i> operation. The effect of this operation in observing nodes is to clear the <i>full/empty</i> bit of the referring memory location, thus making it reusable.                                        |

Table 3: Additional bus transactions in the MESI protocol

Figure 12: MESI protocol integrated with fine-grain synchronization (implicit full/empty states)

A new signal (referred as c in Figure 12) is introduced in order to determine whether a synchronized operation misses. This bus signal will be called shared-word signal, as it indicates whether any other node is sharing the referring word. The shared-word signal can be implemented as a wired-OR

controller line, which is asserted by each cache that holds a copy of the relevant word with the *full/empty* bit set. According to this notation, a waiting read request written in the form PrWNRd(C) successfully performs, while an event of the form  $PrWNRd(\overline{C})$  causes a synchronization miss. Note also that, as each cache line may contain several synchronized data words, it is necessary to specify the specific word to which the synchronized operation is to be performed. Consequently, a negated synchronization signal  $(\overline{C})$  causes a requesting read to be appended to the list of pending operations whereas a requesting write to be performed successfully. If the synchronization signal is otherwise asserted (C), then a synchronized read is completed successfully whereas a requesting write is suspended.

In addition to the shared-word signal already introduced, three more wired-OR signals are required for the protocol to operate correctly, as described in [30]. The first signal (named s) is asserted if any processor different than the requesting processor has a copy of the cache line. The second signal is asserted if any cache has the block in a dirty state. This signal modifies the meaning of the former in the sense that an existing copy of a cache line has been modified and then all the copies in other nodes are invalid. A third signal is necessary in order to indicate whether all the caches have completed their snoop, that means, if it is reliable to read the value of the first two signals.

Figure 12 shows a more compact state transition specification in which information about the *full/empty* state of the accessed word is implicit. Instead, the value of the c line or the *full/empty* bit is specified as a required condition between parentheses. Figure 11 and Figure 12 do not consider neither transient states needed for bus acquisition nor the effects due to real signal delays.

## 4.1. Mapping between processor instructions and bus transactions

When a processing node issues a memory operation, the cache located at that node first interprets the request and, in case of a miss, it later translates the operation into one or more bus transactions. The correspondence between the different processor instructions and the memory requests seen on the bus is shown in Table 4. The same notation as in Figure 2 is used.

Table 4: Correspondence between processor instructions and memory requests

| Request from processor | Bus transaction        |

|------------------------|------------------------|

| PrUNRd                 | BusRd (ordinary read)  |

| PrUNWr                 | BusWr (ordinary write) |

| PrUARd                 | BusRd + BusSCl         |

| PrUAWr                 | BusAWr <sup>3</sup>    |

| PrSNRd                 | BusRd(C) <sup>4</sup>  |

| PrSNWr                 | BusWr(C)               |

| PrSARd                 | BusRd(C) + BusSCl      |

| PrSAWr                 | BusSWr(C)              |

<sup>4</sup> The bus transaction BusRd is in this case used in combination with the shared-copy signal.

23

<sup>&</sup>lt;sup>3</sup> Neither unconditional altering writes nor conditional non-altering writes are considered in the protocol specification.

As seen on Table 4, unconditional non-altering read and write requests generate ordinary read and write transactions on the bus. On the contrary, an unconditional altering read requires a <code>BusRd</code> transaction followed by a <code>BusSCl</code> transaction. Effectively, apart from retrieving the data from the corresponding memory location, a <code>PrUARd</code> request also clears the <code>full/empty</code> state bit of the referring location. This is performed by <code>BusSCl</code>, which does not access nor modifies the data but only the <code>full/empty</code> bit. It is important to observe that an unconditional altering read cannot be performed by <code>just a BusSCl</code> transaction, as it just alters the <code>full/empty</code> bit without retrieving any data. The last unconditional operation, <code>PrUAWr</code>, generates a specific bus transaction, namely <code>BusAWr</code>, which unconditionally sets the <code>full/empty</code> bit after writing the corresponding data to the accessed memory location.

It is inferred from Table 4 that the behavior of all conditional memory operations depends on the value of the shared-word bus signal<sup>5</sup>. A conditional non-altering read, for instance, generates an ordinary read bus transaction after checking whether the shared-bus signal is asserted. A conditional altering read generates a Busscl transaction in addition to the ordinary read transaction. Finally, a conditional altering write causes a Busswr transaction to be initiated on the bus. This transaction sets the *full/empty* bit after writing the corresponding data to the referred memory location.

Figure 13: Sample scenario of mapping between processor instructions and bus transactions

Note that all synchronized operations generate the same bus transactions regardless of their particular type (waiting, non-faulting or faulting). The difference resides in the behavior when a synchronization miss is detected and not in the bus transactions issued as a consequence of the request. A sample scenario is shown in the figure below.

-

<sup>&</sup>lt;sup>5</sup> This behavior is systematically specified in section 4.3.

## 4.2. Management of pending requests

Each processing node keeps a local deferred list. This list holds both ordinary presence misses and synchronization misses. It is possible also for both types of misses to happen for a single access. In this case, not only the accessed line is not present in the cache, but also the synchronization state is not met at the remote location where the copy of the word is held. After a relevant full/empty bit change is detected, any operation that matches a required synchronization state is resumed at the appropriate processing node.

Table 5 shows how the management of the deferred list local to a node is done. Concretely, the table specifies the action taken when a given request is received with respect to a pending request already present in the list of deferred operations<sup>6</sup>. A c indicates that both requests are conflicting and thus need to be kept separated into two different entries, always ensuring that local order is maintained. On the contrary, an M means that both requests can be merged and thus treated as a sole request from the point of view of memory accesses.

Pending request (already in MSHR) PrUARd PrWARd PrUNRd PrWNRd PrNNRd PrNARd PrTNRd PrTARd PrUNRd М М М М М М М М PrUARd Μ М М М М Μ PrWNRd С С С С Incoming request С С С PrWARd С Μ Μ Μ Μ PrNNRd Μ С Μ С Μ С Μ С PrNARd Μ С Μ С Μ С Μ С С С С С PrTNRd М М М M PrTARd М С С С С Μ М M

Table 5: Management of coalescing requests

As a rule of thumb, a pending write is conflicting with any incoming request, so it can never be merged and requires a separate entry in the list of pending requests<sup>7</sup>. As they are always conflicting, all write requests have been excluded from Table 5. Another important observation is that pending altering reads can only be merged with unconditional operations. Additionally, all non-altering pending read request can be coalesced with any other incoming read request.

Apart from coalescing of requests, it is also crucial to specify how resuming of pending requests is done. As explained at the beginning of this section, coherence of full/empty state bits is ensured by

$^{7}$  It could be possible to make read requests be satisfied by pending writes to the same location. However, this introduces extra complexity in the memory unit in order to meet the consistency model. A write request cannot be

satisfied by a pending read request in any case.

<sup>&</sup>lt;sup>6</sup> The simulation model only considers PrsnRd, Prsawr and Pruacl instructions.

proper bus transactions, to be precise, Busswr and Busscl. This means that all caches that have pending requests for a given memory location will know when the synchronization condition is met by snooping into the bus and waiting for a Busswr or a Busscl transaction. When such transaction is noticed, a comparator checks if there is an entry in any MSHR matching the received bus transaction. In this case, action is taken so as to resume the pending request.

Due to this feature, it is possible for a cache to have pending requests for a memory location that is not cached or is cached in an *invalid* state. The location will be brought again into the cache when the synchronization miss is solved. The ability of replacing cache lines that have pending requests allows efficient management and resuming of pending requests with minimum risk of saturating the cache hierarchy.

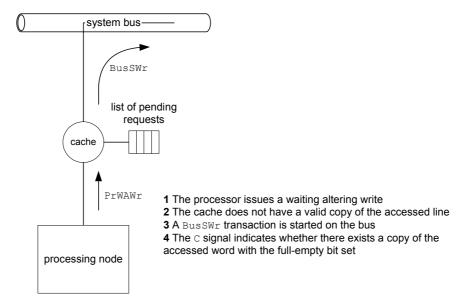

Figure 14: Resuming of pending requests

A representative scenario is shown in Figure 14, in which three nodes have pending requests to a location (x) in their MSHR. While nodes A and B have invalid copies in their caches, node C has the exclusive ownership of the referred location, whose *full/empty* state bit is unset. After node C successfully performs a conditional altering write to location x, this event is notified on the bus by a Busswr transaction. This transaction informs nodes A and B that they can resume the pending request to location x, which happens to be a conditional altering read. As a consequence, only one of these nodes will be able to successfully issue the operation at this point. This is imposed by bus order. For instance, if node B gets the bus ownership before node A, the pending request from the former will be resumed and the operation at node A will stay pending in the MSHR.

### 4.3. Transition rules

A detailed explanation of the new transition rules from each coherence state is presented in the following sections. A description in the form of c-styled *pseudo-code* is also presented in each case. Observe that, as with the ordinary coherence misses, the ordering of synchronization misses from different processors is imposed by bus order.

#### 4.3.1. Invalid state

```

SWITCH(incomingRequest) {

CASE PrUNRd: send(BusRd);

IF (S) {

flushFromOtherCache();

nextState = shared;

readFromMemory();

nextState = exclusive;

BREAK;

CASE PrUNWr: send(BusRdX);

nextState = modified;

BREAK:

CASE PrWNRd: send(BusRd);

IF (S && C) {

flushFromOtherCache();

nextState = shared;

} ELSE IF (!S && C) {

readFromMemory();

nextState = exclusive;

} ELSE {

addToDeferredList(); // Wait.

BREAK;

CASE PrWAWr: send(BusSWr);

IF (S && !C) {

writeToBus();

nextState = shared;

} ELSE IF (!S && !C) {

// To be evaluated at simulation.

writeToCache();

nextState = modified;

} FLSE {

addToDeferredList(); // Wait.

BREAK;

CASE PrUAC1: IF (C) {

send(BusSCl);

nextState = invalid;

BREAK;

```

A successful conditional waiting read request from the local processor (PrWNRd) leads either to the *exclusive-clean* state (if no other cache holds a copy of the block) or to the *shared* state (if more caches have a copy of the accessed block). In any case, a BusRd transaction is generated in order to fetch the data from the corresponding cache or shared memory location. However, if the synchronization condition is not met ( $\overline{C}$ ), then the request is appended to the local deferred list and the state is not changed. This occurs when neither the caches nor the shared memory assert the C line.

Cache-to-cache transfers are needed when data is modified in one ore more caches and the copy in the shared memory is stale. An alternative is to flush the modified data back to memory and then to the node that requested access, but this approach is obviously slower than the former.

A successful waiting write request from the local processor (PrwAwr) leads either to the *modified* state (if no other cache holds a copy of the block) or to the *shared* state (if more caches have a copy of the block). This implies a performance improvement since the next successful synchronized operation to the same cache slot will necessarily be a read and a state transaction will be saved. If the synchronization condition is not met (the line C is asserted), then the operation is suspended.

A PrUAC1 request generates a Bussc1 transaction but does not load the block into cache. This is a design alternative and will be evaluated at the simulation stage of this study.

#### 4.3.2. Modified state

If the *full/empty* bit is set, a conditional waiting read (PrwNRd) retrieves the data from the local cache and generates no bus transaction. Otherwise, the request is appended to the local deferred list.

A conditional waiting write (PrWAWr) fails if the C line is asserted and sets the *full/empty* bit otherwise. In the latter, a Busswr transaction is generated and the relevant pending requests in the local deferred list are resumed. The effect of a Busswr in the other caches is precisely to set the *full/empty* bit and to analyze their deferred list so as to resume the relevant pending requests.

A Pruacl request generates a Busscl transaction and unsets the *full/empty* bit. This transaction does not flush the block from cache. This is a design alternative and will be evaluated at the simulation stage of this study.

```

SWITCH(incomingRequest) {

Processor requests

CASE PrUNRd: readFromCache();

nextState = modified;

BREAK;

CASE PrUNWr: writeToCache();

nextState = modified;

BREAK;

CASE PrWNRd: IF (full) {

readFromCache();

nextState = modified;

} FLSE {

addToDeferredList();

nextState = modified;

BREAK:

CASE PrWAWr: send(BusSWr);

IF (empty) {

writeToCache();

resumePendingReqs();

nextState = modified;

} ELSE {

addToDeferredList():

nextState = modified;

BREAK;

CASE PrUAC1: IF (full) {

unsetFE();

nextState = modified;

BREAK;

// Bus signals

CASE BusRd: flush();

nextState = shared;

```

<sup>8</sup> If a transition to the modified state is performed as in the ordinary MESI protocol, an additional BusRdX transaction is then required on the bus.

### 4.3.3. Exclusive-clean state

```

SWITCH(incomingRequest) {

// Processor requests

CASE PrUNRd: readFromCache();

nextState = exclusive;

BREAK;

CASE PrUNWr: writeToCache();

nextState = modified;

BREAK;

CASE PrWNRd: IF (full) {

readFromCache();

nextState = exclusive;

} ELSE {

addToDeferredList();

nextState = exclusive;

BREAK;

CASE PrWAWr: send(BusSWr);

IF (empty) {

writeToCache();

resumePendingReqs();

nextState = shared; // To be evaluated at simulation.

} ELSE {

addToDeferredList();

nextState = exclusive;

BREAK;

CASE PrUAC1: IF (full) {

unsetFE();

nextState = modified;

BREAK;

// Bus signals

CASE BusRd: flush();

nextState = shared;

BREAK;

CASE BusRdX: flush();

nextState = invalid;

BREAK;

CASE BusSWr: IF (empty) {

writeToCache();

resumePendingReqs();

nextState = shared;

BREAK;

CASE BusSCl: IF (full) {

unsetFE();

nextState = shared;

BREAK;

```

As no other caches hold a copy of this block, a synchronized read (PrWNRd) leads to the same coherence state.

#### 4.3.4. Shared state

```

SWITCH(incomingRequest) {

// Processor requests

CASE Prunkd: readFromCache();

nextState = shared;

BREAK:

CASE PrUNWr: send(BusRdX);

writeToCache();

nextState = modified;

BREAK;

CASE PrWNRd: IF (full) {

readFromCache();

nextState = shared;

} ELSE {

addToDeferredList();

nextState = shared;

BREAK;

CASE PrWAWr: send(BusSWr);

IF (empty) {

writeToCache();

resumePendingReqs();

nextState = shared; // To be evaluated at simulation.

} ELSE {

addToDeferredList();

nextState = shared;

BREAK;

CASE PrUAC1: IF (full) {

unsetFE();

send(BusSCl);

nextState = shared;

BREAK;

// Bus signals

CASE BusRd: flush();

nextState = shared;

BREAK;

CASE BusRdX: flush();

nextState = invalid;

BREAK:

CASE BusSWr: IF (empty) {

writeToCache();

resumePendingReqs();

nextState = shared;

BREAK;

CASE BusSCl: IF (full) {

unsetFE();

nextState = shared;

BREAK:

```

The same rules apply as for the modified state, with the only exception of the Busswr and Busscl bus transactions, which do not cause a state transition in this case.

## 4.4. Summary

A bus based coherence protocol with fine-grain synchronization support has been introduced. A systematic protocol description is made in the form of state diagrams and *pseudo-code*. Although this implementation considers only waiting non-altering reads and waiting altering writes, the behavior of other memory operations is derived in a straightforward manner, as it is a simplified version of the former.

One of the base ideas of the protocol is that *full/empty* state bit coherence is maintained by bus transactions defined for this purpose, namely <code>BussWr</code> and <code>BussCl</code>. An additional bus signal called

shared-word is also introduced in order to implement the conditional behavior of synchronizing operations.

A drawback of integrating fine-grain synchronization support at the cache level is the complexity of managing pending synchronization requests. Rules for coalescing and resuming synchronizing requests have been explained in detail. It is expected that this supplementary complexity does not translate in excessive hardware overhead, as most of the required hardware is already present in modern multiprocessors. Consequently, application software making use of synchronizing memory operations will likely experience a noteworthy performance improvement without the need of extensive hardware deployment.

## 5. Integration with directory-based protocols

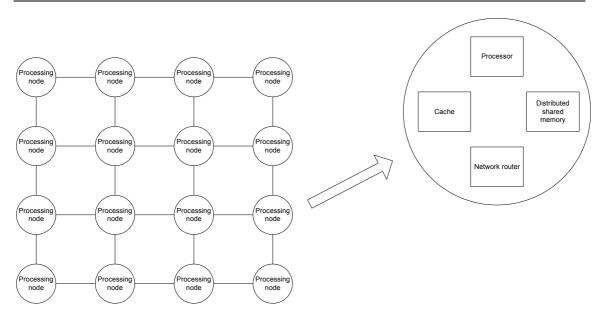

Figure 15: Mesh network-based architecture

In a network-based system, such the one shown in Figure 15, each shared memory block has a directory entry that lists the nodes that have a cached copy of the data. *Full/empty* bits are stored as an extra field in the coherence directory entry. *Point-to-point* messages are used to keep the directory up-to-date and to request permission for a load or a store to a particular location.

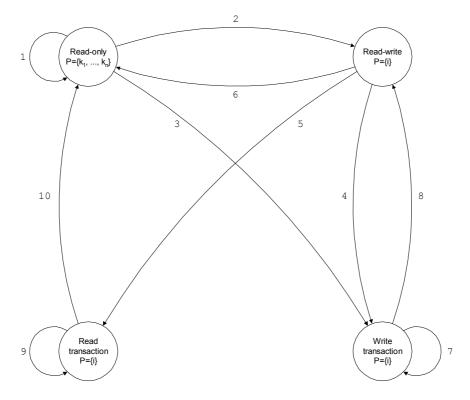

Figure 16: Alewife's coherence protocol state diagram

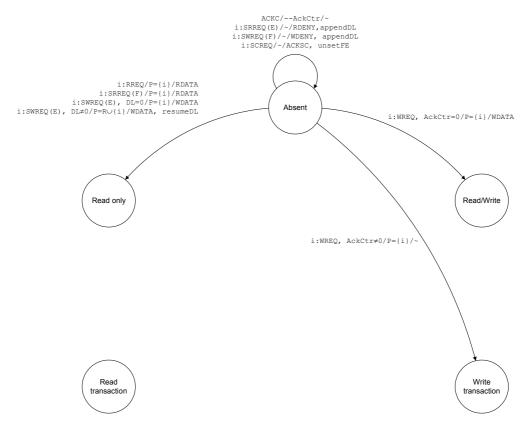

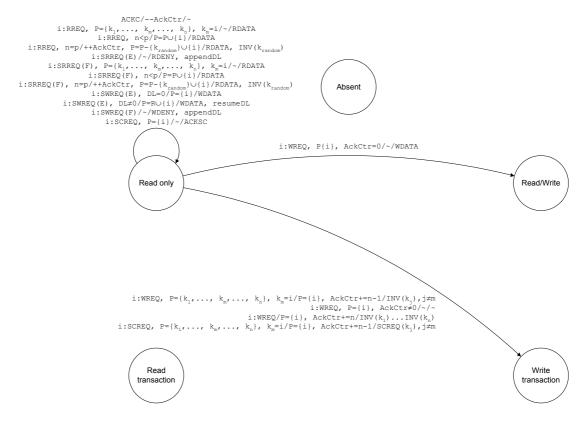

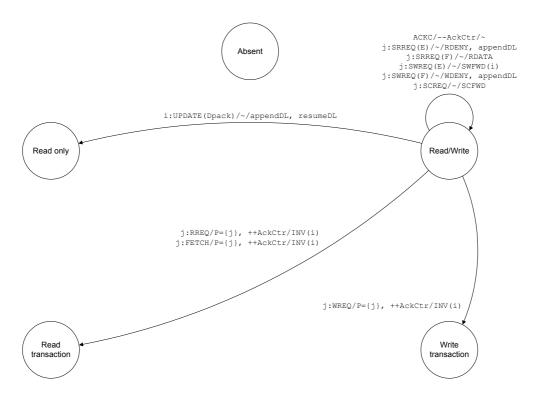

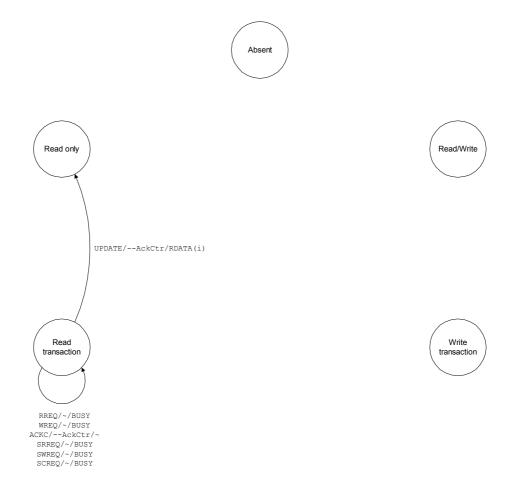

The description made here is based on Alewife's coherence protocol [24]. Our model considers a limited directory protocol, thus restricting the amount of simultaneous copies of a memory block. The following states are defined in Alewife's coherence protocol:

- Read-Only: One or more caches have a read-only copy of the block.

- Read-Write: Only one cache has a read-write copy of the block.

- Read Transaction: Cache is holding a read request (update in progress).

- Write Transaction: Cache is holding a write request (invalidation in progress).

The state diagram corresponding to this protocol is shown in Figure 16. The semantics of the transitions depicted in this figure are resumed in Table 6 [50].

Table 6: Semantics of the transitions in the directory-based protocol

| Label | Input message                   | Output message           |

|-------|---------------------------------|--------------------------|

| 1     | i → RREQ                        | RDATA → i                |

|       | $i \rightarrow FETCH$           | RDATA → i                |

| 2     | $i \rightarrow WREQ$            | WDATA → i                |

|       | $i \rightarrow MREQ$            | $MODG \rightarrow i$     |

| 3     | $i \rightarrow WREQ$            | INVR $\rightarrow$ $k_j$ |

|       | $i \rightarrow MREQ$            | INVR $\rightarrow$ $k_j$ |

| 4     | $i \rightarrow WREQ$            | INVW $\rightarrow$ i     |

|       | $i \rightarrow MREQ$            | INVW $\rightarrow$ i     |

| 5     | $j \rightarrow RREQ$            | INVW $\rightarrow$ i     |

|       | $j \rightarrow FETCH$           | INVW $\rightarrow$ i     |

| 6     | $i \rightarrow REPM$            | -                        |

| 7     | $j \rightarrow RREQ$            | BUSY → j                 |

|       | $j \rightarrow WREQ$            | BUSY → j                 |

|       | $j \rightarrow MREQ$            | BUSY → j                 |

|       | j $ ightarrow$ FETCH            | BUSY → j                 |

|       | $j \rightarrow ACKC$            | _                        |

| 8     | j → ACKC                        | WDATA $ ightarrow$ i     |

|       | $j \rightarrow REPM$            | WDATA → i                |

|       | $j \rightarrow \mathtt{UPDATE}$ | WDATA $ ightarrow$ i     |

| 9     | $j \rightarrow RREQ$            | BUSY → j                 |

|       | $j \rightarrow WREQ$            | BUSY → j                 |

|       | j → MREQ                        | BUSY → j                 |

|       | $j \rightarrow FETCH$           | BUSY → j                 |

| 10    | j → ACKC                        | RDATA → i                |

|       | j → REPM                        | RDATA → i                |

|       | $j \rightarrow \mathtt{UPDATE}$ | RDATA → i                |

Although Alewife provides support for fine-grain synchronization, these mechanisms are implemented over the cache coherence protocol, which works as if *full/empty* bits do not exist. The cache controller in Alewife has limited hardware support for *full/empty* bits storage. Concretely, these bits are saved as an extra field in the cache tags. This has two advantages. First, the memory used to store cache

data does not need to have odd word-length. Second, access to the cache data is slower than access to the cache tags.

When the processor requests a memory access, the *Communications and Memory Management Unit* (CMMU) determines whether the access is local or remote. The CMMU also checks if the access implies a synchronizing operation by analyzing the ASI value in the memory operation. The address corresponding to the access is checked against the cache tags file, and both the appropriate tag and the *full/empty* bit are retrieved. At this point one of the following actions is executed<sup>9</sup>:

- a context switch is executed if the access produces a cache miss,

- a full/empty trap is fired in the case of a synchronization fault,

- otherwise, the operation is completed successfully.

According to the performance measures made in Alewife, the overhead of successful synchronizing operations is not significant [46]. When a synchronization miss is detected, a trap is fired and the corresponding thread either polls the location until the synchronization condition is met or blocks according to a given waiting algorithm. While no additional hardware is required for polling, blocking needs to save and restore context registers. The latter case is notably expensive, as loads take two cycles and stores take three cycles.

By integrating synchronization mechanisms with the coherence protocol, the complexity introduced by thread scheduling is avoided. Instead, synchronization misses are handled similarly to ordinary cache misses. As the hardware needed to deal with the latter has already the capability to store part of the information associated with a synchronization miss, it is expected that the hardware overhead introduced by integrating synchronization mechanisms with cache coherence is not excessive.

## 5.1. Mapping between processor instructions and network transactions

The network transactions used in the proposed protocol are explained in Table 7, which shows both messages sent from a cache to memory and requests sent back from memory to a cache.

Six new messages are introduced in order to implement fine-grain synchronization at the cache level. More concretely, these messages are SRREQ, SWREQ, SCREQ from cache to memory and SRDENY, SWDENY and ACKSC from memory to cache.

34

<sup>&</sup>lt;sup>9</sup> In all cases, the retrieved *full/empty* bit is placed into the external condition codes so that the processor has access to it

Type of message **Symbol Semantics** RREO request to read a word that is not in the cache WREQ request to write a word SRREO waiting and non-altering read request Cache to Memory SWREQ waiting and altering write request SCREQ request to clear the full/empty bit UPDATE returns modified data to memory ACKC acknowledges that a word has been invalidated RDATA contains a copy of data in memory (response to RREQ) WDATA contains a copy of data in memory (response to  $\mathtt{WREQ})$ SRDENY sent if a SRREQ misses; the requesting cache will retry at a later stage SWDENY sent if a SWREQ misses; the requesting cache will retry at a Memory to Cache later stage TNV invalidates cached words ACKSC acknowledges that the full/empty bit has been unset in all the copies of the block BUSY response to any RREQ or WREQ while invalidations are in progress

Table 7: Network transactions in the directory-based protocol

As proposed in [74], some fields are needed in the coherence protocol messages in order to integrate fine-grain synchronization. We will make use of some of these proposed additional fields. Specifically, the following fields are required:

- slot's index in the cache line which is being accessed,

- slots in the home directory copy whose list of pending requests is empty; this allows saving protocol messaged in some cases where a block is in the read-write state (see section 5.3.3 for more details),

- deferred lists in remote caches are sent to the home node when they release the exclusive ownership; this scenario is further explained in section 5.2.

When a processing node issues a memory operation, the cache located at that node interprets the request and translates it into one or more network transactions. The correspondence between the different processor instructions and memory requests sent over the network is shown below.

Table 8: Correspondence between processor instructions and memory requests

| Instruction from | Initiated network |

|------------------|-------------------|

| processor        | transactions      |

| PrUNRd           | RREQ              |

| PrUNWr           | WREQ              |

| PrUARd           | RREQ + SCREQ      |

| PrUAWr           | -                 |

| PrSNRd           | SRREQ             |

| PrSNWr           | CWREQ             |

| PrSARd           | SRREQ + SCREQ     |

| PrSAWr           | SWREQ             |

## 5.2. Management of pending requests

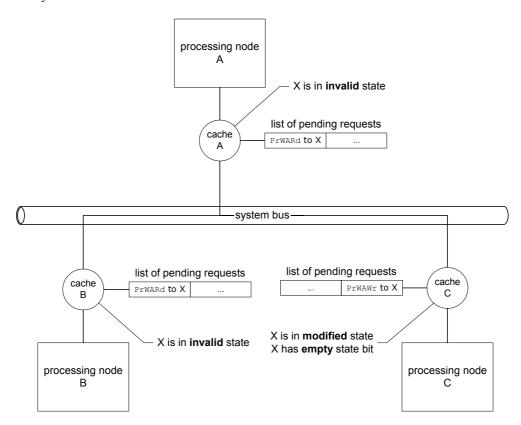

Extensive discussion about different alternatives for managing deferred lists is presented in [75]. We propose a hybrid procedure for managing deferred lists in which lists of pending operations are kept either at the home directory or in a distributed manner, depending on the state of the line to which pending operations refer. The rules for coalescing requests are the same as in Table 5.

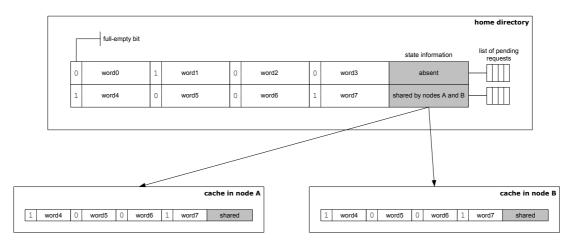

Lists of pending requests for memory locations that are in an absent or read-only state are maintained as an additional field in the corresponding home directory. Effectively, in these states it is not possible to adopt a distributed approach, since after a transition to the read-write state the home directory will need to have knowledge of the type of pending requests and the nodes that issued this requests.

A sample case of this scenario is shown in Figure 17, in which two nodes, namely A and B, share a copy of a given memory block. If another node takes the exclusive ownership of this block, information about pending requests issued by nodes A and B will be lost unless the home directory has knowledge of those requests. A naive approach is to make the directory keep track of only the nodes with pending requests, because this would require informing all of these nodes each time a *full/empty* state change is detected, thus generating extra traffic. Figure 17 also shows a different memory block for which there is no copy at any other node in the system, thus being in the absent state. The same rules apply for this location.

Figure 17: Management of pending requests for an absent or read-only memory block

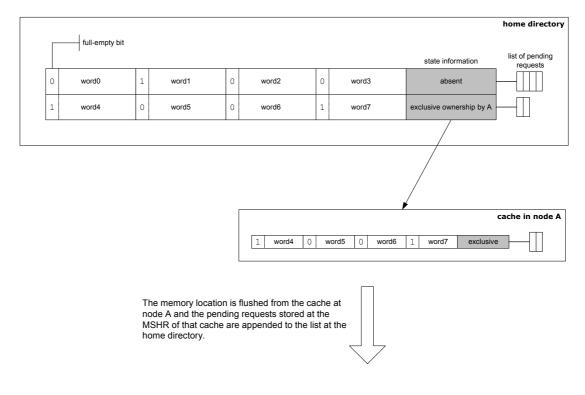

For locations in a read-write state, we adopt a distributed solution in which both the home directory and the remote cache keep track of pending operations. When a remote cache releases its copy of the block, the deferred list kept locally to that cache is sent to the home node and merged with the deferred list at the home directory. The rules for coalescing requests are those in Table 5. An example in which a location is first owned by node A and then flushed from its cache is shown on Figure 18.

<sup>&</sup>lt;sup>10</sup> The absent state indicates that no cache is holding a copy of the referred memory location. Consequently this location does not fall into any of the four states described on page 33.

Figure 18: Management of pending requests for a read-write memory block

As in the bus-based scheme, it is also necessary to specify how resuming of pending requests is done. Contrary to the former, coherence of *full/empty* state bits is not always ensured at the home directory. In fact, the home directory does not have a valid copy of the *full/empty* bit of a memory location that is in the read-write state. In such case, the directory forwards requests from other nodes to the exclusive owner of the block, where they will be serviced. According to these features, resuming of pending requests is based on the following rules:

- if a block is in the absent or read-only state, the home directory is responsible for resuming requests, by checking if there is any entry in the deferred list that matches an incoming transaction,

- if a block is in the read-write state, the cache having the exclusive ownership knows whether there are pending requests for that block at the home directory. In that case, relevant operations performed at that node are forwarded to the home node in order to check if any pending request can be resumed. Otherwise, the deferred list can be locally managed at the exclusive owner.

Consequently, it is not possible for a cache to have pending requests for a memory location that is not cached. These pending requests are kept and managed at the home directory. This solution is a hybrid approach between a *fully distributed* and a *centralized* deferred list management.

### 5.3. Directory transition rules

A detailed explanation of the transition rules from each coherence state is presented in the following sections. A description in the form of C-styled *pseudo-code* is also presented in each case. In the state diagrams, the notation indicated below is used. A tilde symbol (~) is indicated when no side effect or output message is necessary.

processor id: input message, preconditions / side effects / output message, local actions

### 5.3.1. Absent state

```

SWITCH (incomingRequest) {

CASE RREQ(i): addNodeToDirectory(i); // "i" is the sending node id.

send(RDATA, i);

// send requested data to node.

nextState = readOnly;

BREAK;

CASE WREQ(i): IF (ackCounter == 0) {

addNodeToDirectory(i);

send(WDATA, i);

nextState = readWrite;

} ELSE {

addNodeToDirectory(i);

nextState = writeTransaction;

CASE SRREQ(i): IF (full) {

addNodeToDirectory(i);

send(RDATA, i);

nextState = readOnly;

} ELSE {

send(RDENY, i);

addToDeferredList();

nextState = absent;

BREAK:

CASE SWREQ(i): IF (empty && deferredListEmpty()) {

addNodeToDirectory(i);

send(WDATA, i);

nextState = readOnly;

} ELSE IF (empty && !deferredListEmpty()) {

addNodeToDirectory(i);

send(WDATA, i);

resumePendingReqs();

nextState = readOnly;

} ELSE

send(WDENY, i);

addToDeferredList();

nextState = absent;

BREAK;

CASE SCREQ(i): unsetFE();

send(ACKSC, i);

nextState = absent;

BREAK;

CASE ACKC(i): ackCounter--;

nextState = absent;

BREAK:

```

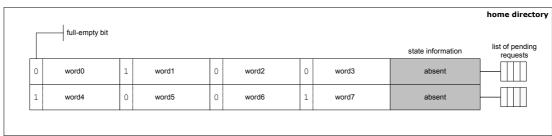

If a SRREQ is received and the synchronization state is met (the FE bit is set), the requesting cache is added to the directory and the requested data is sent in a RDATA message. The state is then changed to read-only. If the SRREQ fails (the FE bit is unset), a RDENY message is sent

back to the requesting cache and the operation is appended to the deferred list in the home node. The state is not changed and the requesting cache waits until the home node solves the synchronization miss and sends back the requested data.

Figure 19: State transitions from the absent state

If a SWREQ is received and the synchronization condition is met (FE is not set), the requesting cache is added to the directory and a WDATA message is sent to it. Any relevant pending request in the local deferred list is resumed and appropriate data is sent to its corresponding cache, which is also added to the directory. The state is then changed to read-only, and not to read-write as it could be expected. This optimization allows other processing nodes to read this data without any state transition. If the *full/empty* bit is set on a SWREQ, then a WDENY is replied and the operation is suspended. The state in the home directory is not changed.

If a SCREQ is received, the *full/empty* bit is reset and an ACKSC sent back to the requesting cache. The state in the home directory is not changed.

#### 5.3.2. Read-only state

```

SWITCH (incomingRequest) {

CASE RREQ(i): IF (hasPointerInDirectory(i)) {

send(RDATA, i); // "i" is the sending node id.

} ELSE IF (!directoryFull()) {

addNodeToDirectory();

send(RDATA, i);

} ELSE {

++ackCounter;

j = evictRandomDirectoryEntry(); // j is the evicted line.

send(INV, j);

addNodeToDirectory();

}

}

```

```

send(RDATA, i);

nextState = readOnly;

BREAK;

CASE WREQ(i):

IF (hasPointerInDirectory(i) && (numberOfEntries() > 1)) {

ackCounter += numberOfEntries() - 1;

FOR (j = 0; j < numberOfEntries(); j++) {

If (i != j)</pre>

send(INV, j);

clearDirectory();

addNodeToDirectory(i);

nextState = writeTransaction;

} ELSE If (hasPointerInDirectory(i)

&& (numberOfEntries() == 1)

&& (ackCounter != 0)) {

nextState = writeTransaction;

} ELSE IF (hasPointerInDirectory(i)

&& (ackCounter == 0)) {

send(WDATA, i);

nextState = readWrite;

} ELSE { // if the line is not in the directory

ackCounter += n;

FOR (j = 0; j < numberOfEntries(); j++) {

send(INV, j);

clearDirectory();

addNodeToDirectory(i);

BREAK:

CASE SRREQ(i): IF (full && hasPointerInDirectory(i)) {

send(RDATA, i);

} ELSE IF (full && !directoryFull()) {

addNodeToDirectory();

send(RDATA, i);

} ELSE IF (full && directoryFull()) {

++ackCounter:

j = evictRandomDirectoryEntry(); // j is the evicted line.

send(INV, j);

addNodeToDirectory();

send(RDATA, i);

} ELSE IF (empty) {

send(RDENY, i);

addToDeferredList();

nextState = readOnly;

BREAK:

CASE SWREQ(i): IF (empty & deferredListEmpty()) {

addNodeToDirectory(i);

send(WDATA, i);

} ELSE IF (empty & !deferredListEmpty()) {

addNodeToDirectory(i);

send(WDATA, i);

resumePendingRegs();

} ELSE {

send(WDENY, i);

addToDeferredList();

nextState = readOnly;

BREAK;

CASE SCREQ(i): IF (numberOfEntries() > 1) {

ackCounter += numberOfEntries() - 1;

FOR (j = 0; j < numberOfEntries(); j++) {

If (i != j)</pre>

send(SCREQ, j);

clearDirectory();

addNodeToDirectory();

nextState = writeTransaction;

} ELSE IF (hasPointerInDirectory(i)) {

unsetFE();

send(ACKSC, i);

nextState = readOnly;

BREAK;

CASE ACKC(i): ackCounter--;

nextState = readOnly;

BREAK;

```

If a SRREQ is received and the synchronization condition is met, an RDENY message is replied and the request is appended to the local deferred list. If the synchronization condition is met and

the requesting cache is already in the directory, an RDATA message is sent back with the requested memory location. If the requesting cache is not in the directory and there are still free directory entries, the cache is added to the directory. Otherwise, a random cache is replaced with the requesting cache and an INV message is sent to the removed cache. The home directory state is not changed in any case.

Figure 20: State transitions from the read-only state

If a SWREQ is received and the *full/empty* is set, then a WDENY message is replied. Otherwise, the requesting cache is added to the directory and a WDATA message is sent back. In any case, the home directory state is not changed.

If a SCREQ is received and no more caches share this block, then the *full/empty* bit is cleared and the request is acknowledged with an ACKSC message. The state is not changed in this case. However, if more caches have a copy of this block, their *full/empty* bits must be reset before acknowledging the operation. Consequently, the state is changed to write-transaction and an SCREQ message is sent to each cache with a copy of the block. Note that the SCREQ operation is particularly time-expensive, as it works as a barrier for all the involved caches.

#### 5.3.3. Read-write state

```

BREAK:

CASE WREQ(j): IF (!hasPointerInDirectory(j)) {

++ackCounter;

send(INV, i);

clearDirectory();

addNodeToDirectory(j);

nextState = writeTransaction;